集成 LCD 驱动+升压的 M0 核微控制器

JS32L010 低功耗系列

用户手册

V1.9

珠海巨晟科技股份有限公司

地 址：广东省珠海市高新区金唐路 1 号港湾 1 号湾 8 栋 4 楼

电 话：0756-3335384 传 真：0756-3335384

网 站：[www.honor-ic.com](http://www.honor-ic.com) 邮 编：519080

## 版本历史

变更类型: A - 增加 M - 修订 D - 删除

| 变更版本号 | 日期         | 变更类型 | 修改人 | 审核  | 摘要                                                                        |

|-------|------------|------|-----|-----|---------------------------------------------------------------------------|

| V1.0  | 2020-3-23  |      |     |     | 正式版本                                                                      |

| V1.1  | 2020-5-11  | M    | RLD | MCW | 更新时序图                                                                     |

| V1.2  | 2020-7-28  | A    | RLD | MCW | Add ssop24                                                                |

| V1.3  | 2020-8-21  | M    | RLD | MCW | 增加 IO 类型说明                                                                |

| V1.4  | 2020-9-10  | M    | RLD | MCW | 修改 ADKEY_CFG :ADCPRE                                                      |

| V1.5  | 2020-9-15  | M    | RLD | YH  |                                                                           |

| V1.6  | 2020-10-15 | M    | RLD | YH  | 修改 GPIOx_OSPEEDL/<br>GPIOx_OSPEEDH                                        |

| V1.7  | 2020-10-23 | M    | RLD |     | 1. 更新 SPI 时序图<br>2. 修改产品主要特性名称：集成<br>LCD 驱动+升压的 M0 核微控制器<br>3. 修正文档错别字和语句 |

| V1.8  | 2021-9-9   | M    | QZH |     | 1. 修改 swd 引脚映射<br>2. 修正文档部分语句<br>3. 增加 UART_DMA_STA 寄存器                   |

| V1.9  | 2021-10-9  | M    | QZH |     | 1.修正 PC9 定义                                                               |

## 版权声明

本资料是为了让用户根据用途选择合适的产品而提供的参考资料，不转让属于珠海巨晟科技股份有限公司或者第三方所有的知识产权以及其他权利的许可。在使用本资料所记载的信息并对有关产品是否适用做出最终判断前，请您务必把所有信息作为一个整体系统来评价。对于本资料所记载的信息使用不当而引起的损害、责任问题或者其他损失，珠海巨晟科技股份有限公司将不承担责任。未经珠海巨晟科技股份有限公司的许可，不得翻印或者复制全部或部分本资料的内容。

今后日常产品的更新会在适当的时候发布，恕不另行通知。在购买本资料所记载的产品时，请预先向珠海巨晟科技股份有限公司确认最新信息，并请您通过各种方式关注珠海巨晟

科技股份有限公司公布的信息。

如果您需要了解有关本资料所记载的信息或产品的详情，请与珠海巨晟科技股份有限公司的技术服务部门联系，我们会为您提供全方位的技术支持。

珠海巨晟科技股份有限公司

# 目录

|                                        |    |

|----------------------------------------|----|

| <b>1 产品特性</b> .....                    | 1  |

| <b>2 产品简介</b> .....                    | 2  |

| 2.1 典型应用.....                          | 2  |

| 2.2 选型表.....                           | 2  |

| 2.3 命名规则.....                          | 2  |

| <b>3 终端配置与功能</b> .....                 | 3  |

| 3.1 管脚图.....                           | 3  |

| 3.2 管脚定义.....                          | 5  |

| <b>4 系统及存储器架构</b> .....                | 10 |

| 4.1 系统架构.....                          | 10 |

| 4.2 存储器映射.....                         | 11 |

| <b>5 嵌入式闪存 (FLASH)</b> .....           | 14 |

| 5.1 闪存主要特性.....                        | 14 |

| 5.2 闪存功能描述.....                        | 14 |

| <b>6 中断和事件(INT/EVT)</b> .....          | 24 |

| 6.1 嵌套向量中断控制器.....                     | 24 |

| 6.2 系统滴答(SysTick)校准值寄存器.....           | 24 |

| 6.3 中断功能描述.....                        | 24 |

| 6.4 外部中断/事件控制器(EXTI).....              | 25 |

| <b>7 循环冗余校验计算单元 (CRC)</b> .....        | 26 |

| 7.1 简介.....                            | 26 |

| 7.2 模块框图.....                          | 26 |

| 7.3 主要特性.....                          | 26 |

| 7.4 寄存器定义.....                         | 26 |

| 7.5 操作流程.....                          | 27 |

| <b>8 电源管理 (POWER MANAGEMENT)</b> ..... | 29 |

| 8.1 电源.....                            | 29 |

| 8.2 电源管理器.....                         | 29 |

| 8.3 电源控制寄存器.....                       | 30 |

| <b>9 低功耗(LOW POWER)</b> .....          | 32 |

| 9.1 低功耗模式.....                         | 32 |

| 9.2 进入低功耗.....                         | 32 |

| 9.3 低功耗唤醒.....                         | 32 |

| <b>10 复位和时钟控制 (RESET/CLOCK)</b> .....  | 34 |

| 10.1 引脚复位(MCLR)功能.....                 | 34 |

| 10.2 复位.....                           | 34 |

| 10.3 时钟.....                           | 35 |

| <b>11 通用输入输出 (GPIO)</b> .....          | 37 |

| 11.1 简介.....                           | 37 |

| 11.2 模块框图.....                         | 37 |

| 11.3 GPIO 主要特征.....                    | 37 |

| 11.4 GPIO 功能描述.....                    | 37 |

| 11.5 GPIO 寄存器描述.....                   | 40 |

| <b>12 通信接口外设 (CSI)</b> .....           | 47 |

| 12.1 串行外设接口和内部集成电路(SPI_IIC).....       | 47 |

| 12.2 SPI/IIC 寄存器描述.....                | 50 |

| <b>13 通用异步收发器 (UART)</b> .....         | 57 |

| 13.1 简介.....                           | 57 |

| 13.2 模块框图.....                         | 57 |

| 13.3 UART 特性.....                      | 57 |

| 13.4 IO 映射.....                        | 57 |

| 13.5 寄存器描述.....                        | 58 |

|                                     |            |

|-------------------------------------|------------|

| <b>14 比较器 (COMP).....</b>           | <b>64</b>  |

| 14.1 简介.....                        | 64         |

| 14.2 主要特性.....                      | 64         |

| 14.3 寄存器描述.....                     | 65         |

| 14.4 操作流程.....                      | 65         |

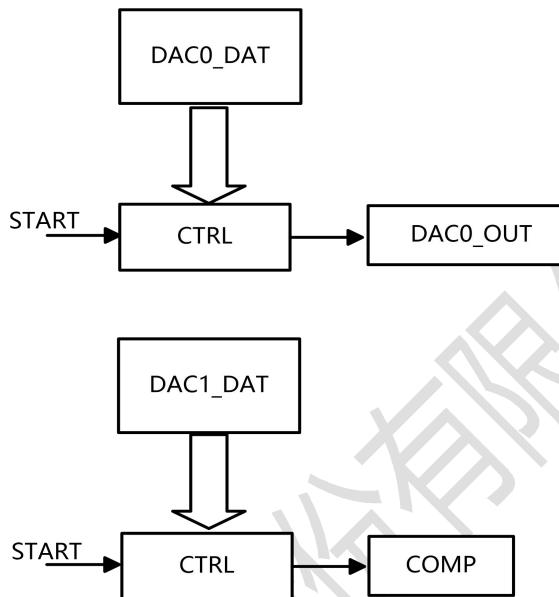

| <b>15 数模转换器 (DAC).....</b>          | <b>66</b>  |

| 15.1 简介.....                        | 66         |

| 15.2 模块框图.....                      | 66         |

| 15.3 主要特征.....                      | 66         |

| 15.4 寄存器描述.....                     | 66         |

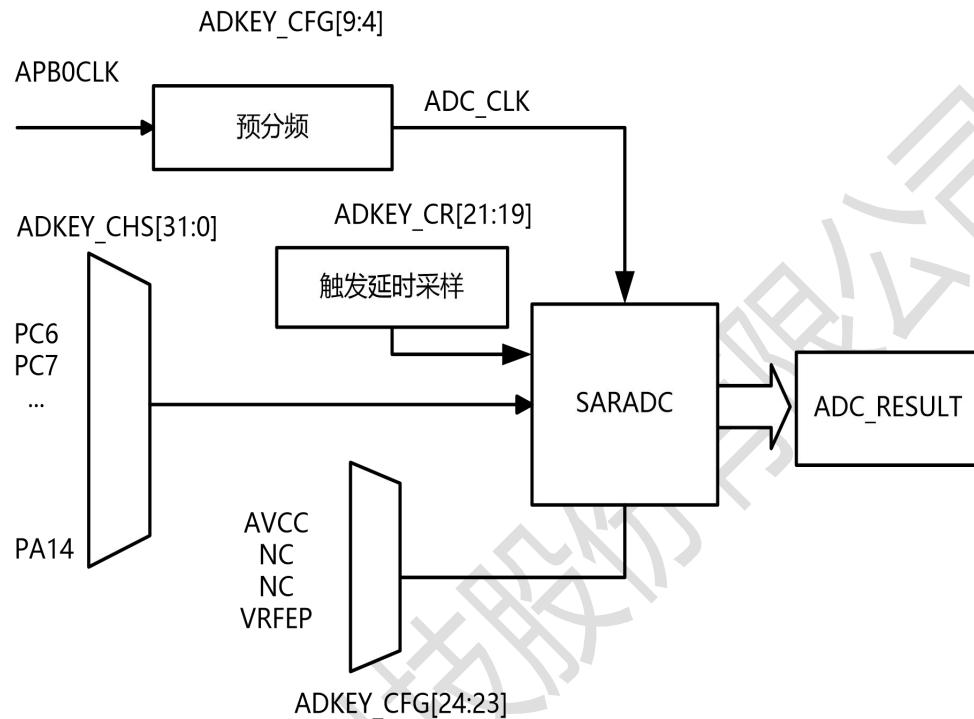

| <b>16 模数转换器 (ADC).....</b>          | <b>67</b>  |

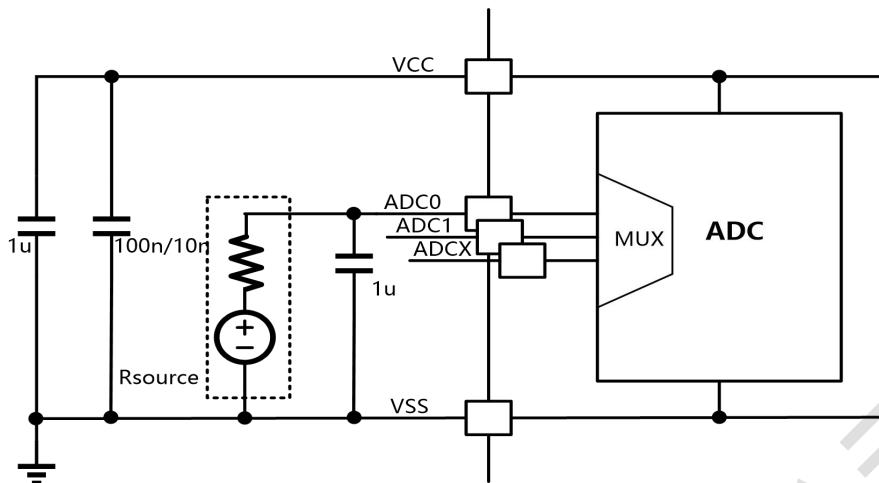

| 16.1 功能简介.....                      | 67         |

| 16.2 模块框图.....                      | 67         |

| 16.3 主要特征.....                      | 67         |

| 16.4 功能描述.....                      | 67         |

| 16.5 通道选择.....                      | 68         |

| 16.6 寄存器描述.....                     | 69         |

| 16.7 操作流程.....                      | 73         |

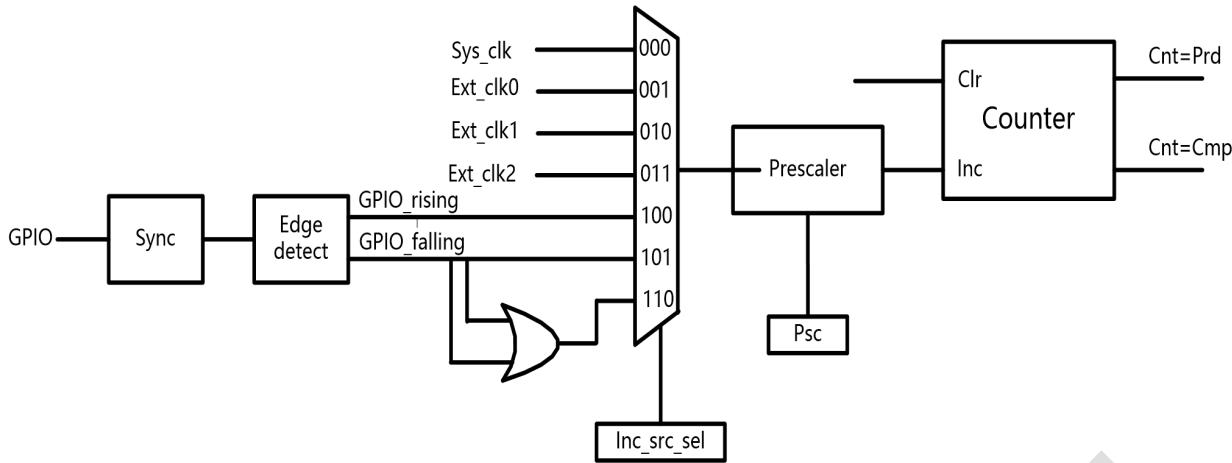

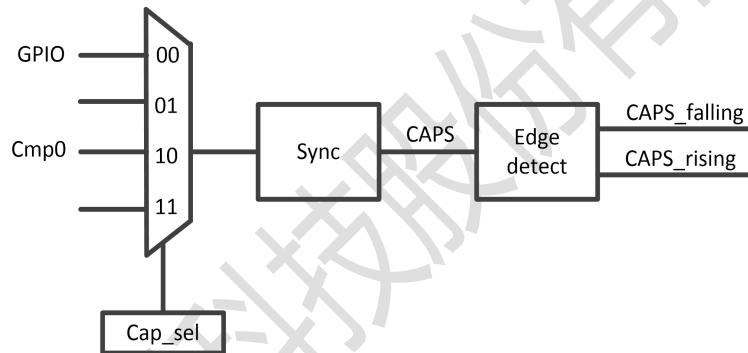

| <b>17 定时器 (TMR0/1/2/3/4/5).....</b> | <b>75</b>  |

| 17.1 16 位定时器 0/1/2/3/5.....         | 75         |

| <b>18 看门狗 (WDT).....</b>            | <b>87</b>  |

| 18.1 简介.....                        | 87         |

| 18.2 模块框图.....                      | 87         |

| 18.3 寄存器描述.....                     | 87         |

| <b>19 系统寄存器 (SYSTEM REG).....</b>   | <b>89</b>  |

| 19.1 系统寄存器基址表.....                  | 89         |

| 19.2 寄存器描述.....                     | 89         |

| <b>20 液晶控制器 (LCD).....</b>          | <b>104</b> |

| 20.1 简介.....                        | 104        |

| 20.2 功能框图.....                      | 104        |

| 20.3 主要特性.....                      | 104        |

| 20.4 原理介绍.....                      | 104        |

| 20.5 寄存器描述.....                     | 109        |

| <b>21 实时时钟 (RTC).....</b>           | <b>118</b> |

| 21.1 简介.....                        | 118        |

| 21.2 功能框图.....                      | 118        |

| 21.3 寄存器描述.....                     | 119        |

| 21.4 使用说明.....                      | 123        |

| <b>22 频率锁相环 (PLL).....</b>          | <b>124</b> |

| 22.1 功能简介.....                      | 124        |

| 22.2 寄存器描述.....                     | 124        |

| <b>23 器件电子签名 (E-SIGNATURE).....</b> | <b>126</b> |

| 23.1 存储器容量寄存器.....                  | 126        |

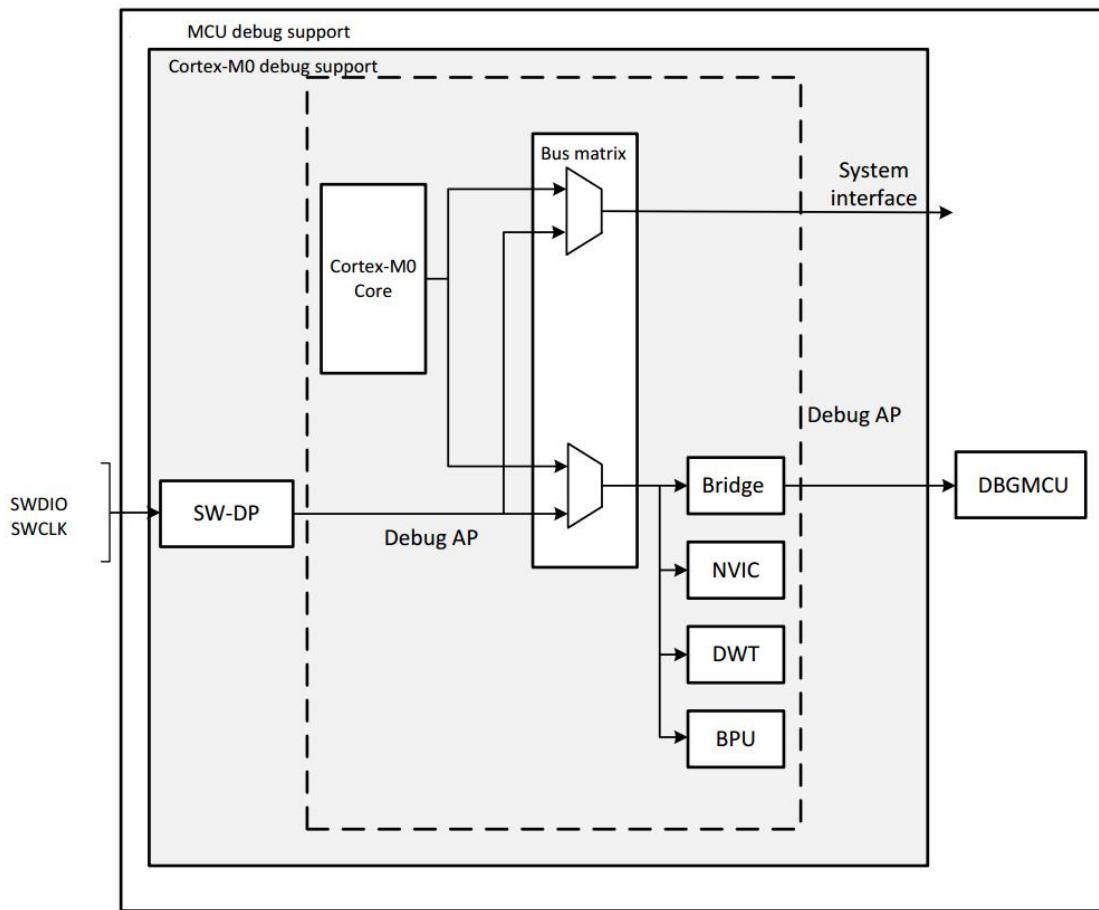

| <b>24 调试支持 (DBG).....</b>           | <b>127</b> |

| 24.1 引脚分布和调试端口脚.....                | 127        |

| 24.2 SWD 调试端口脚.....                 | 127        |

| 24.3 SW 调试端口.....                   | 128        |

| 24.4 MCU 调试.....                    | 129        |

| <b>25 电气特性.....</b>                 | <b>130</b> |

| 25.1 绝对最大额定值.....                   | 130        |

| 25.2 工作条件/特性参数.....                 | 130        |

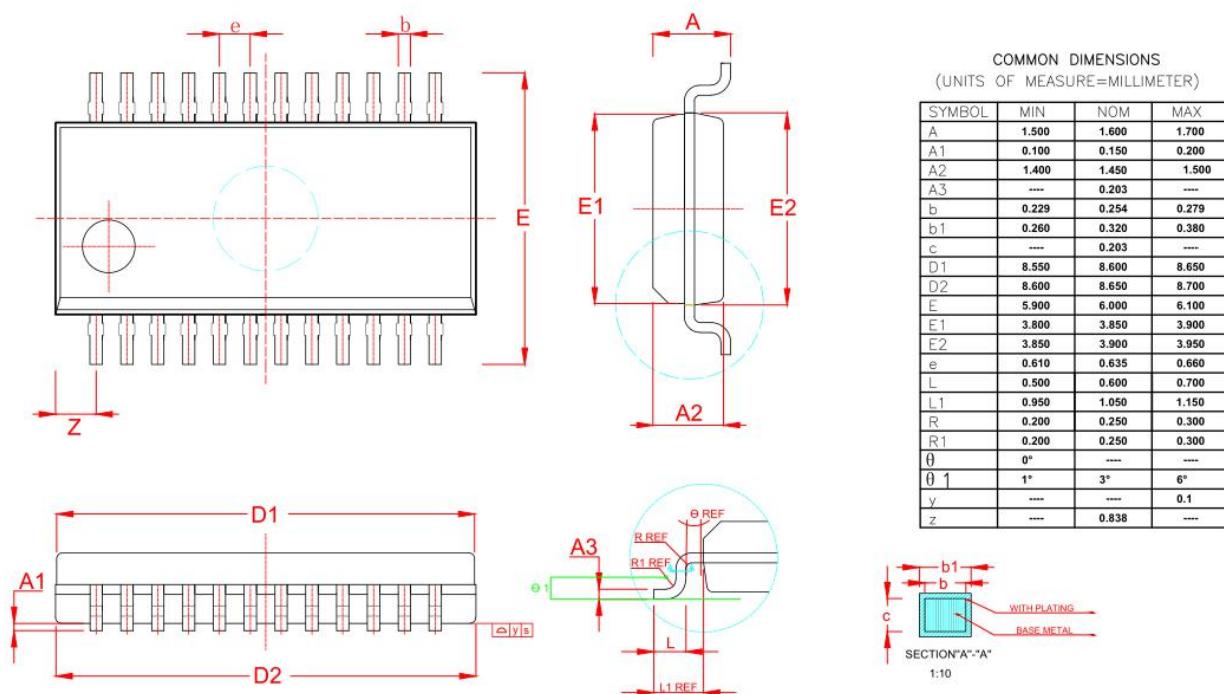

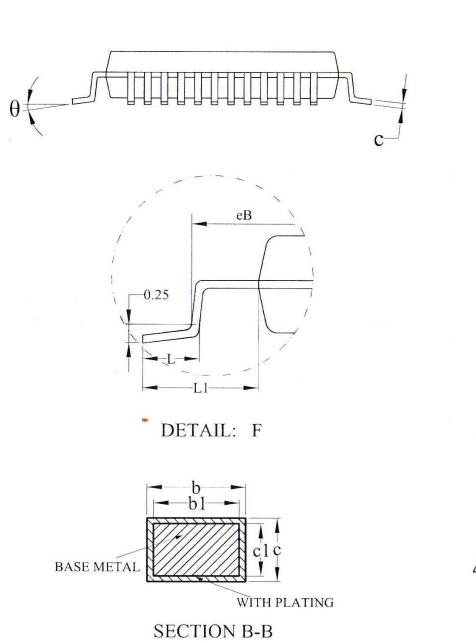

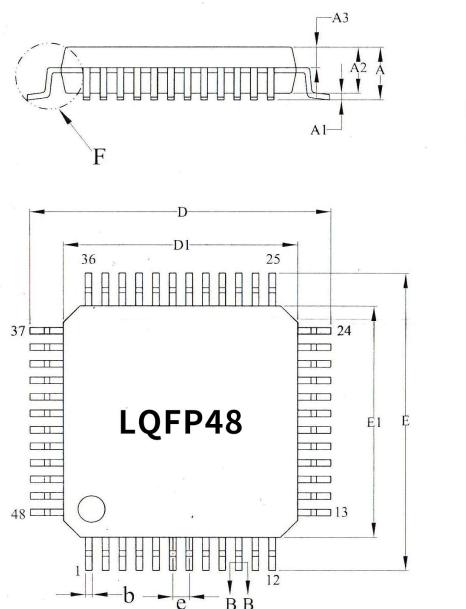

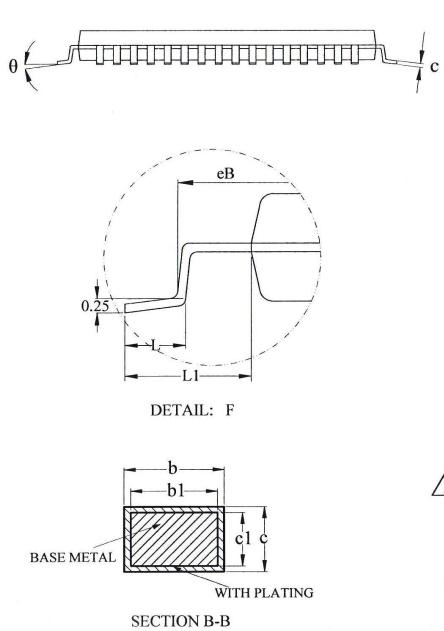

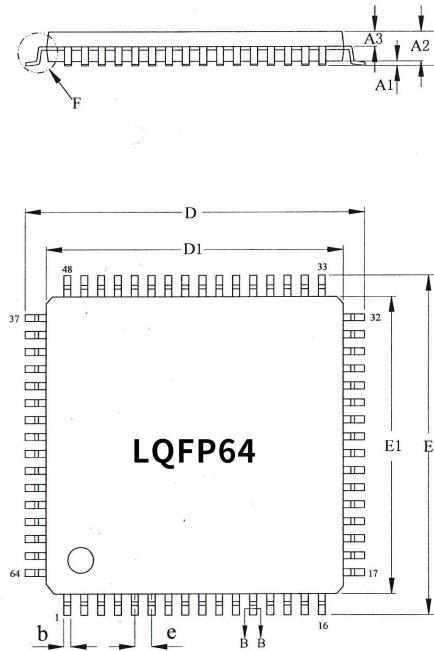

| <b>26 封装信息.....</b>                 | <b>141</b> |

| 26.1 LQFP48.....                    | 141        |

|                  |     |

|------------------|-----|

| 26.2 LQFP64..... | 141 |

| 26.3 SSOP24..... | 142 |

珠海巨晟科技股份有限公司

## 1 产品特性

- **内核与系统**

- 32 位 ARM® Cortex™-M0 处理器内核

- 最高工作频率可达 48MHz

- 32 个指令周期 32 位硬件乘法器

- 32 个中断源, 可配置 4 层中断优先级

- 支持 SWD 调试接口

- **存储器**

- 32K 字节的闪存程序存储器

- 2K 字节的 SRAM

- Boot loader 支持片内 Flash、支持单线 UART、在线用户编程(IAP)/系统编程(ISP)

- **时钟、复位和电源管理**

- 1.8V ~ 3.6V 供电

- 片上电容 LDO 为芯片内系统供电, LDO 带过流保护

- 上电/断电复位(POR/PDR)、16 档可编程电压监测器(PVD)

- 外部 32.768KHz 晶体振荡器

- 内嵌 26MHz( $\pm 1.5\%$ ) 高速振荡器

- 内嵌低速振荡器 32.768KHz( $\pm 1.5\%$ )

- PLL 支持 CPU 最高运行在 48MHz

- 内嵌 128KHz 启动低速振荡器

- 内置时钟安全系统(CSS)

- **DMA 支持**

- 支持的外设: EFLASH, UART, SPI, CRC, ADC, TIMER1

- **多达 57(LQFP64) /41(LQFP48)个快速 I/O 端口**

- 所有 I/O 口可以触发边沿或电平响应中断, 唤醒低功耗模式

- 支持一个输出低电压大电流 IO(漏电流 500mA)

- **通讯接口外设**

- 1 路 SPI, master 下最高支持 26Mbit/s, 支持 1/2/4 线主从模式, 支持 I2C 模式

- 1 路 UART, 支持程序升级和多机通讯

- **LCD 显示控制器**

- 最大支持 COM+SEG 数量是 42 个, COM 个数不大于 8 个, SEG 不大于 38 个

- 支持静态扫描和动态扫描

- 动态扫描 duty: 1/1, 1/2, 1/3, 1/4, 1/5, 1/6, 1/7, 1/8

- 动态扫描偏置电压: 1/2, 1/3

- 允许软件随时更新显存数据, 不影响显示效果

- 支持内部升压电源给 LCD 供电, 内部电阻分压和外部电源直接给 LCD 供电

- 支持对比度调节和低功耗模式显示

- **支持闪烁功能**

- **扫描频率为 30Hz~120Hz 可调**

- **实时时钟 RTC**

- 数字时钟补偿

- 硬件万年历

- 支持 12 小时、24 小时显示模式

- 两个可编程闹钟

- 低功耗工作

- **8 个定时器**

- 5 个 16 位定时器, 1 个 32 位定时器, 每个定时器支持 1 个 IC/OC, 可组合用于 IR 控制编码, 支持 PWM 输出

- 1 个看门狗定时器

- 1 个系统时间定时器: 24 位自减型计数器

- **高安全性**

- 支持硬件加解密程序, 防止程序被盗

- 支持 5/7/8/16/32 位 CRC 校验, 保证数据准确性

- **低功耗模式**

- 支持 IDLE, STOP, SLEEP 模式

- 8.52mA@IDLE: 3.3V, PLL 48MHz, LCD 显示, 等待按键唤醒, 不关时钟, 外设运行, CPU 停止

- 2.89mA@STOP: 3.3V, LCD 显示, 等待按键唤醒, 数字模块时钟关闭, CPU 停止

- 7.8uA@SLEEP: 3.3V, LCD 显示, 等待按键唤醒, 除 32KHz 其它时钟关闭, CPU 停止

- 2.2uA@SLEEP: 3.3V, 没有其它外设, 等待按键唤醒, 所有时钟关闭, CPU 停止

- 唤醒时间最快 10us

- GPIO 口可通过边沿或电平触发中断唤醒

- **1 个 12 位高速模数转换器**

- 支持最高 250K 采样率

- 26 个通道@LQFP64, 13 个通道@LQFP48

- 转换范围: 0 ~  $V_{VREFP}$

- **1 个比较器**

- **1 个 8 位精度 DAC, 1 个 12 位精度 DAC**

- **内置温度传感器**

- **高可靠性**

- ESD HBM 4KV

- EFT  $\pm 4KV$

- Latch-up  $\pm 200mA$  @105°C

- **96 位的芯片唯一 ID(UID)**

- **封装**

- LQFP48/LQFP64/SSOP24

- **工业级温度范围**

- -40°C ~ 105°C

## 2 产品简介

JS32L010 系列是超低功耗，最高 48MHz 主频的 32 位 ARM Cortex M0 微控制器。它集成了 12 位 250K 转换率高精度 ADC, DAC, 比较器, CRC, 支持 PWM 的定时器, LCD 显示, UART, SPI, IIC 等通讯外设, 还支持硬件加解密程序, 保护代码安全。具有在线仿真, 高集成度, 高抗干扰性, 高可靠性和超低功耗的特点。

### 2.1 典型应用

- 额/耳温枪、血糖/血压/血氧/心电监测仪等医疗电子产品

- 儿童玩具、电子烟、酒精测试仪、按摩仪等消费电子产品

- 遥控器、火警探头, 温控器、智能门锁等智能传感器产品

- 各种对于电池供电和对于功耗苛求的便携式设备等

### 2.2 选型表

| 产品型号         | 封装     | Flash | RAM | GPIO | LCD<br>(COM*SEG)                 | Timer              | PWM | RTC | UART | SPI/I <sup>2</sup> C | ADC<br>12bit | DAC               | 比较<br>器 | 温度传<br>感器 | 大电流 IO |

|--------------|--------|-------|-----|------|----------------------------------|--------------------|-----|-----|------|----------------------|--------------|-------------------|---------|-----------|--------|

| JS32L010L5L7 | LQFP48 | 32K   | 2K  | 41   | 8*34/6*36/<br>5*37/4*38<br>..... | 5*16bit<br>1*32bit | 6   | 1   | 1    | 1                    | 13ch         | 1*8bit<br>1*12bit | 1       | ±2°C      | 1      |

| JS32L010P5L7 | LQFP64 | 32K   | 2K  | 57   |                                  |                    |     |     |      |                      | 26ch         |                   |         |           |        |

| JS32L010E5O7 | SSOP24 | 32K   | 2K  | 22   |                                  |                    |     |     |      |                      | 6ch          |                   |         |           |        |

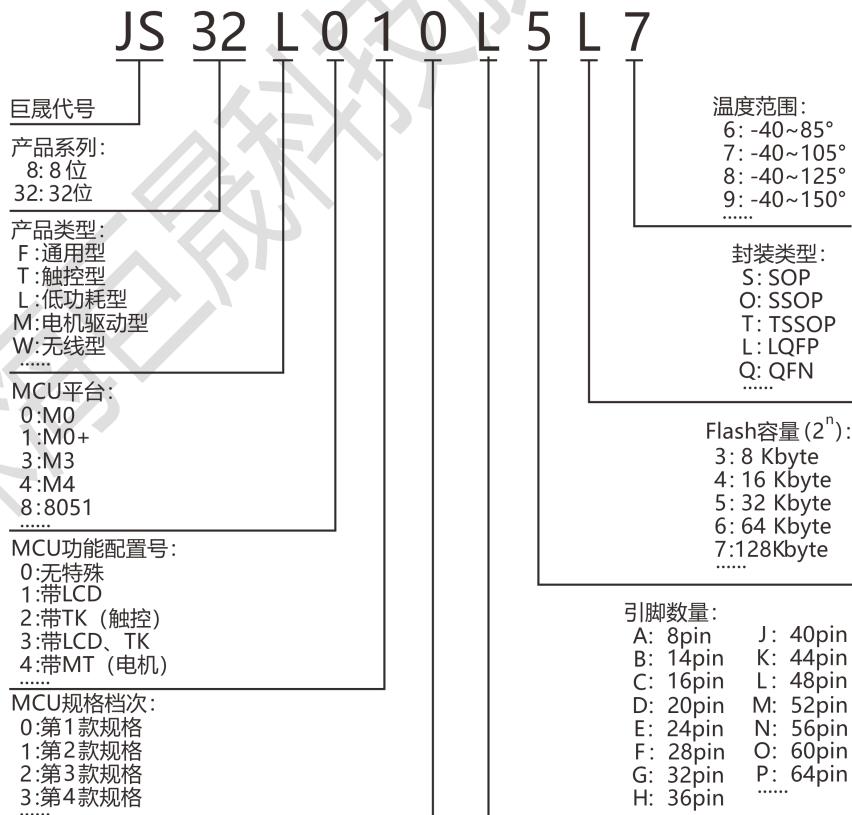

### 2.3 命名规则

### 3 终端配置与功能

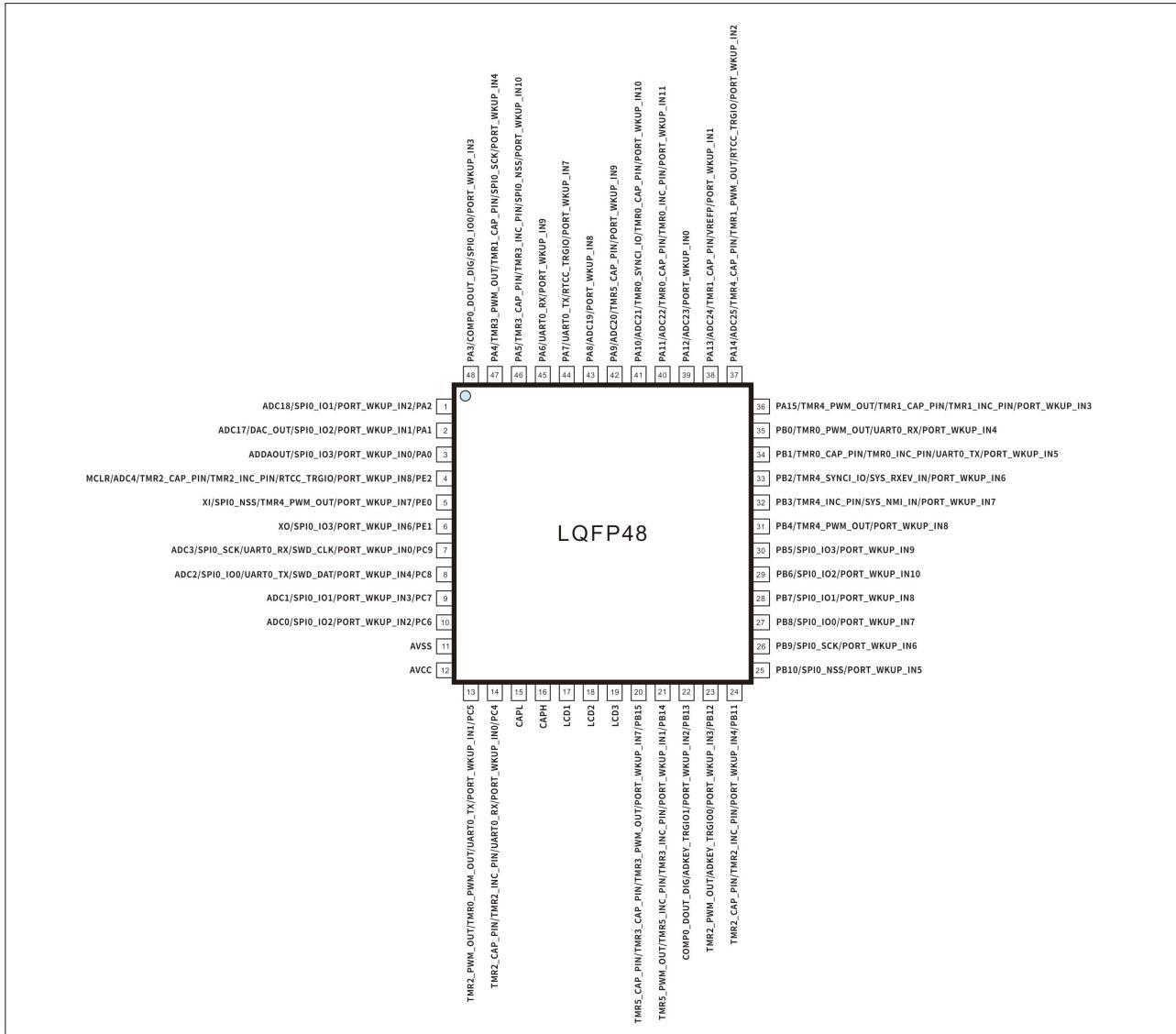

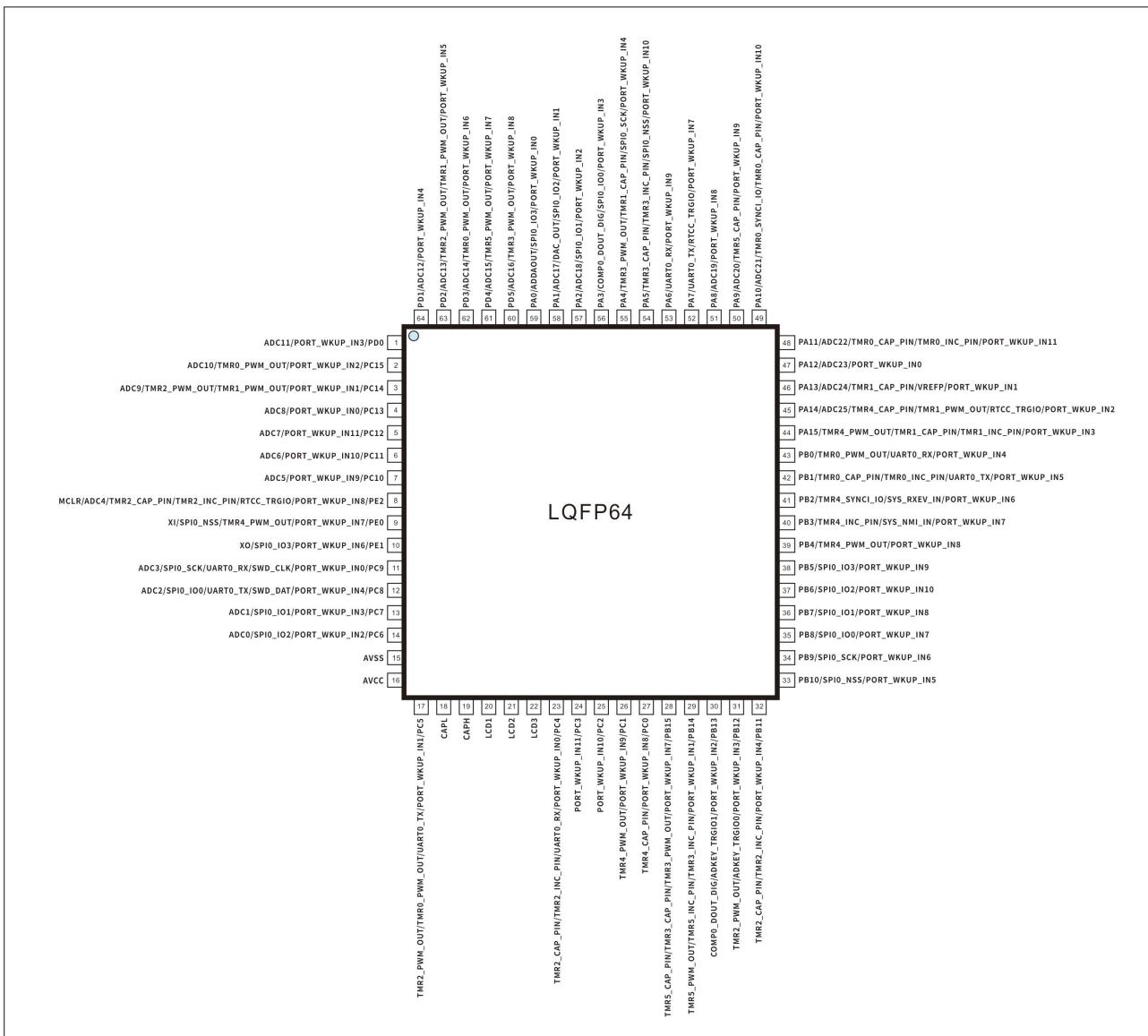

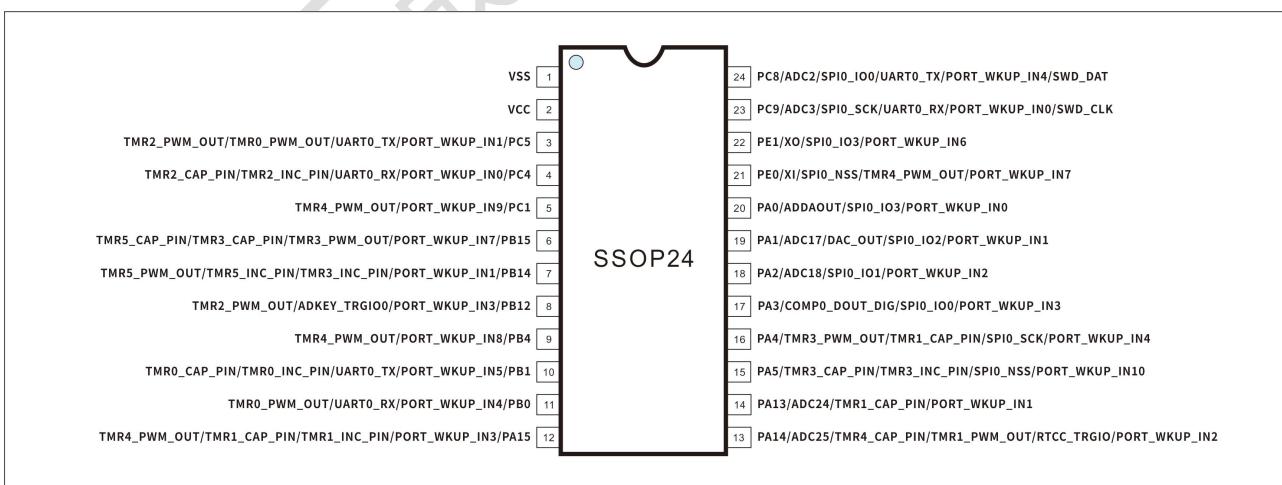

#### 3.1 管脚图

图 3-1 JS32L010 LQFP48 Package

图 3-2 JS32L010 LQFP64 Package

图 3-3 JS32L010 SSOP24 Package

### 3.2 管脚定义

表 3-1 GPIO 管脚定义

| LQFP48 | LQFP64 | SSOP24 | 引脚   | 引脚类型 | I/O 电路类型  | 复用功能                                                        | 额外功能             |

|--------|--------|--------|------|------|-----------|-------------------------------------------------------------|------------------|

| 3      | 59     | 20     | PA0  | I/O  | LCDIO[0]  | SPI0_IO3<br>PORT_WKUP_IN0                                   | ADDAOUT          |

| 2      | 58     | 19     | PA1  | I/O  | LCDIO[1]  | SPI0_IO2<br>PORT_WKUP_IN1                                   | ADC17<br>DAC_OUT |

| 1      | 57     | 18     | PA2  | I/O  | LCDIO[2]  | SPI0_IO1<br>PORT_WKUP_IN2                                   | ADC18            |

| 48     | 56     | 17     | PA3  | I/O  | LCDIO[3]  | COMPO_DOUT_DIG<br>SPI0_IO0<br>PORT_WKUP_IN3                 | -                |

| 47     | 55     | 16     | PA4  | I/O  | LCDIO[4]  | TMR3_PWM_OUT<br>TMR1_CAP_PIN<br>SPI0_SCK<br>PORT_WKUP_IN4   | -                |

| 46     | 54     | 15     | PA5  | I/O  | LCDIO[5]  | TMR3_CAP_PIN<br>TMR3_INC_PIN<br>SPI0_NSS<br>PORT_WKUP_IN10  | -                |

| 45     | 53     | -      | PA6  | I/O  | LCDIO[6]  | UART0_RX<br>PORT_WKUP_IN9                                   | -                |

| 44     | 52     | -      | PA7  | I/O  | LCDIO[7]  | UART0_TX<br>RTCC_TRGIO<br>PORT_WKUP_IN7                     | -                |

| 43     | 51     | -      | PA8  | I/O  | LCDIO[8]  | PORT_WKUP_IN8                                               | ADC19            |

| 42     | 50     | -      | PA9  | I/O  | LCDIO[9]  | TMR5_CAP_PIN<br>PORT_WKUP_IN9                               | ADC20            |

| 41     | 49     | -      | PA10 | I/O  | LCDIO[10] | TMR0_SYNC1_IO<br>TMR0_CAP_PIN<br>PORT_WKUP_IN10             | ADC21            |

| 40     | 48     | -      | PA11 | I/O  | LCDIO[11] | TMR0_CAP_PIN<br>TMR0_INC_PIN<br>PORT_WKUP_IN11              | ADC22            |

| 39     | 47     | -      | PA12 | I/O  | LCDIO[12] | PORT_WKUP_IN0                                               | ADC23            |

| 38     | 46     | 14     | PA13 | I/O  | LCDIO[13] | TMR1_CAP_PIN<br>PORT_WKUP_IN1                               | ADC24<br>VREFP   |

| 37     | 45     | 13     | PA14 | I/O  | LCDIO[14] | TMR4_CAP_PIN<br>TMR1_PWM_OUT<br>RTCC_TRGIO<br>PORT_WKUP_IN2 | ADC25            |

| 36     | 44     | 12     | PA15 | I/O  | LCDIO[15] | TMR4_PWM_OUT<br>TMR1_CAP_PIN<br>TMR1_INC_PIN                | -                |

|    |    |    |      |     |           |                                                               |   |

|----|----|----|------|-----|-----------|---------------------------------------------------------------|---|

|    |    |    |      |     |           | PORT_WKUP_IN3                                                 |   |

| 35 | 43 | 11 | PB0  | I/O | LCDIO[16] | TMR0_PWM_OUT<br>UART0_RX<br>PORT_WKUP_IN4                     | - |

| 34 | 42 | 10 | PB1  | I/O | LCDIO[17] | TMR0_CAP_PIN<br>TMR0_INC_PIN<br>UART0_TX<br>PORT_WKUP_IN5     | - |

| 33 | 41 | -  | PB2  | I/O | LCDIO[18] | TMR4_SYNC1_IO<br>SYS_RXEV_IN<br>PORT_WKUP_IN6                 | - |

| 32 | 40 | -  | PB3  | I/O | LCDIO[19] | TMR4_INC_PIN<br>SYS_NMI_IN<br>PORT_WKUP_IN7                   | - |

| 31 | 39 | 9  | PB4  | I/O | LCDIO[20] | TMR4_PWM_OUT<br>PORT_WKUP_IN8                                 | - |

| 30 | 38 | -  | PB5  | I/O | LCDIO[21] | SPI0_IO3<br>PORT_WKUP_IN9                                     | - |

| 29 | 37 | -  | PB6  | I/O | LCDIO[22] | SPI0_IO2<br>PORT_WKUP_IN10                                    | - |

| 28 | 36 | -  | PB7  | I/O | LCDIO[23] | SPI0_IO1<br>PORT_WKUP_IN8                                     | - |

| 27 | 35 | -  | PB8  | I/O | LCDIO[24] | SPI0_IO0<br>PORT_WKUP_IN7                                     | - |

| 26 | 34 | -  | PB9  | I/O | LCDIO[25] | SPI0_SCK<br>PORT_WKUP_IN6                                     | - |

| 25 | 33 | -  | PB10 | I/O | LCDIO[26] | SPI0_NSS<br>PORT_WKUP_IN5                                     | - |

| 24 | 32 | -  | PB11 | I/O | LCDIO[27] | TMR2_CAP_PIN<br>TMR2_INC_PIN<br>PORT_WKUP_IN4                 | - |

| 23 | 31 | 8  | PB12 | I/O | LCDIO[28] | TMR2_PWM_OUT<br>ADKEY_TRGIO0<br>PORT_WKUP_IN3                 | - |

| 22 | 30 | -  | PB13 | I/O | LCDIO[29] | COMPO_DOUT_DIG<br>ADKEY_TRGIO1<br>PORT_WKUP_IN2               | - |

| 21 | 29 | 7  | PB14 | I/O | LCDIO[30] | TMR5_PWM_OUT<br>TMR5_INC_PIN<br>TMR3_INC_PIN<br>PORT_WKUP_IN1 | - |

| 20 | 28 | 6  | PB15 | I/O | LCDIO[31] | TMR5_CAP_PIN<br>TMR3_CAP_PIN<br>TMR3_PWM_OUT<br>PORT_WKUP_IN7 | - |

| -  | 27 | -  | PC0  | I/O | LCDIO[32] | TMR4_CAP_PIN<br>PORT_WKUP_IN8                                 | - |

| -  | 26 | 5  | PC1  | I/O | LCDIO[33] | TMR4_PWM_OUT                                                  | - |

|    |    |    |      |     |                         |                                                             |                 |

|----|----|----|------|-----|-------------------------|-------------------------------------------------------------|-----------------|

|    |    |    |      |     |                         | PORT_WKUP_IN9                                               |                 |

| -  | 25 | -  | PC2  | I/O | LCDIO[34]               | PORT_WKUP_IN10                                              | -               |

| -  | 24 | -  | PC3  | I/O | LCDIO[35]               | PORT_WKUP_IN11                                              | -               |

| 19 | 22 | -  | LCD3 | S   | -                       | -                                                           | -               |

| 18 | 21 | -  | LCD2 | S   | -                       | -                                                           | -               |

| 17 | 20 | -  | LCD1 | S   | -                       | -                                                           | -               |

| 16 | 19 | -  | CAPH | S   | -                       | -                                                           | -               |

| 15 | 18 | -  | CAPL | S   | -                       | -                                                           | -               |

| 14 | 23 | 4  | PC4  | I/O | LCDIO[36]               | TMR2_CAP_PIN<br>TMR2_INC_PIN<br>UART0_RX<br>PORT_WKUP_IN0   | -               |

| 13 | 17 | 3  | PC5  | I/O | CURRENTIO/<br>LCDIO[37] | TMR2_PWM_OUT<br>TMR0_PWM_OUT<br>UART0_TX<br>PORT_WKUP_IN1   | -               |

| 12 | 16 | 2  | AVCC | S   | -                       | -                                                           | -               |

| 11 | 15 | 1  | AVSS | S   | -                       | -                                                           | -               |

| 10 | 14 | -  | PC6  | I/O | LCDIO[38]               | SPI0_IO2<br>PORT_WKUP_IN2                                   | ADC0            |

| 9  | 13 | -  | PC7  | I/O | LCDIO[39]               | SPI0_IO1<br>PORT_WKUP_IN3                                   | ADC1            |

| 8  | 12 | 24 | PC8  | I/O | LCDIO[40]               | SPI0_IO0<br>UART0_TX<br>PORT_WKUP_IN4                       | ADC2<br>SWD_DAT |

| 7  | 11 | 23 | PC9  | I/O | LCDIO[41]               | SPI0_SCK<br>UART0_RX<br>PORT_WKUP_IN0                       | ADC3<br>SWD_CLK |

| 6  | 10 | 22 | PE1  | I/O | IOG1                    | SPI0_IO3<br>PORT_WKUP_IN6                                   | XO              |

| 5  | 9  | 21 | PE0  | I/O | IOG1                    | SPI0_NSS<br>TMR4_PWM_OUT<br>PORT_WKUP_IN7                   | XI              |

| 4  | 8  | -  | PE2  | I/O | IOG1                    | TMR2_CAP_PIN<br>TMR2_INC_PIN<br>RTCC_TRGIO<br>PORT_WKUP_IN8 | MCLR<br>ADC4    |

| -  | 7  | -  | PC10 | I/O | IOG1                    | PORT_WKUP_IN9                                               | ADC5            |

| -  | 6  | -  | PC11 | I/O | IOG1                    | PORT_WKUP_IN10                                              | ADC6            |

| -  | 5  | -  | PC12 | I/O | IOG1                    | PORT_WKUP_IN11                                              | ADC7            |

| -  | 4  | -  | PC13 | I/O | IOG1                    | PORT_WKUP_IN0                                               | ADC8            |

| -  | 3  | -  | PC14 | I/O | IOG1                    | TMR2_PWM_OUT<br>TMR1_PWM_OUT<br>PORT_WKUP_IN1               | ADC9            |

| -  | 2  | -  | PC15 | I/O | IOG1                    | TMR0_PWM_OUT<br>PORT_WKUP_IN2                               | ADC10           |

| -  | 1  | -  | PD0  | I/O | IOG1                    | PORT_WKUP_IN3                                               | ADC11           |

| -  | 64 | -  | PD1  | I/O | IOG1                    | PORT_WKUP_IN4                                               | ADC12           |

|   |    |   |     |     |      |                                               |       |

|---|----|---|-----|-----|------|-----------------------------------------------|-------|

| - | 63 | - | PD2 | I/O | IOG1 | TMR2_PWM_OUT<br>TMR1_PWM_OUT<br>PORT_WKUP_IN5 | ADC13 |

| - | 62 | - | PD3 | I/O | IOG1 | TMR0_PWM_OUT<br>PORT_WKUP_IN6                 | ADC14 |

| - | 61 | - | PD4 | I/O | IOG1 | TMR5_PWM_OUT<br>PORT_WKUP_IN7                 | ADC15 |

| - | 60 | - | PD5 | I/O | IOG1 | TMR3_PWM_OUT<br>PORT_WKUP_IN8                 | ADC16 |

注：IOG1 和 LCDIO 属于 A/B 类 IO, CURRENTIO 属于 C 类 IO.

表 3-2 GPIO 复用功能 AF0~AF3

| Port | AF0  | AF1            | AF2          | AF3            |

|------|------|----------------|--------------|----------------|

| PA   | PA0  | -              | SPI0_IO3     | PORT_WKUP_IN0  |

|      | PA1  | -              | SPI0_IO2     | PORT_WKUP_IN1  |

|      | PA2  | -              | SPI0_IO1     | PORT_WKUP_IN2  |

|      | PA3  | COMP0_DOUT_DIG | SPI0_IO0     | PORT_WKUP_IN3  |

|      | PA4  | TMR3_PWM_OUT   | TMR1_CAP_PIN | SPI0_SCK       |

|      | PA5  | TMR3_CAP_PIN   | TMR3_INC_PIN | SPI0_NSS       |

|      | PA6  | -              | UART0_RX     | -              |

|      | PA7  | -              | UART0_TX     | RTCC_TRGIO     |

|      | PA8  | -              | -            | PORT_WKUP_IN7  |

|      | PA9  | -              | -            | PORT_WKUP_IN8  |

|      | PA10 | TMR0_SYNC1_IO  | -            | TMR5_CAP_PIN   |

|      | PA11 | TMR0_CAP_PIN   | TMR0_INC_PIN | PORT_WKUP_IN9  |

|      | PA12 | -              | -            | PORT_WKUP_IN10 |

|      | PA13 | -              | TMR1_CAP_PIN | -              |

|      | PA14 | TMR4_CAP_PIN   | TMR1_PWM_OUT | RTCC_TRGIO     |

|      | PA15 | TMR4_PWM_OUT   | TMR1_CAP_PIN | TMR1_INC_PIN   |

| PB   | PB0  | TMR0_PWM_OUT   | -            | UART0_RX       |

|      | PB1  | TMR0_CAP_PIN   | TMR0_INC_PIN | UART0_TX       |

|      | PB2  | TMR4_SYNC1_IO  | SYS_RXEN_IN  | -              |

|      | PB3  | TMR4_INC_PIN   | SYS_NMI_IN   | -              |

|      | PB4  | TMR4_PWM_OUT   | -            | PORT_WKUP_IN8  |

|      | PB5  | -              | SPI0_IO3     | -              |

|      | PB6  | -              | SPI0_IO2     | -              |

|      | PB7  | -              | SPI0_IO1     | -              |

|      | PB8  | -              | SPI0_IO0     | -              |

|      | PB9  | -              | SPI0_SCK     | -              |

|      | PB10 | -              | SPI0_NSS     | -              |

|      | PB11 | TMR2_CAP_PIN   | TMR2_INC_PIN | PORT_WKUP_IN5  |

|      | PB12 | TMR2_PWM_OUT   | ADKEY_TRGIO0 | PORT_WKUP_IN4  |

|      | PB13 | COMP0_DOUT_DIG | ADKEY_TRGIO1 | PORT_WKUP_IN3  |

|      | PB14 | TMR5_PWM_OUT   | TMR5_INC_PIN | PORT_WKUP_IN2  |

|    |      |              |              |              |                |

|----|------|--------------|--------------|--------------|----------------|

|    | PB15 | TMR5_CAP_PIN | TMR3_CAP_PIN | TMR3_PWM_OUT | PORT_WKUP_IN7  |

| PC | PC0  | TMR4_CAP_PIN | -            | -            | PORT_WKUP_IN8  |

|    | PC1  | TMR4_PWM_OUT | -            | -            | PORT_WKUP_IN9  |

|    | PC2  | -            | -            | -            | PORT_WKUP_IN10 |

|    | PC3  | -            | -            | -            | PORT_WKUP_IN11 |

|    | PC4  | TMR2_CAP_PIN | TMR2_INC_PIN | UART0_RX     | PORT_WKUP_IN0  |

|    | PC5  | TMR2_PWM_OUT | TMR0_PWM_OUT | UART0_TX     | PORT_WKUP_IN1  |

|    | PC6  | SPI0_IO2     | -            | -            | PORT_WKUP_IN2  |

|    | PC7  | SPI0_IO1     | -            | -            | PORT_WKUP_IN3  |

|    | PC8  | SPI0_IO0     | -            | UART0_TX     | PORT_WKUP_IN4  |

|    | PC9  | SPI0_SCK     | -            | UART0_RX     | PORT_WKUP_IN0  |

|    | PC10 | -            | -            | -            | PORT_WKUP_IN9  |

|    | PC11 | -            | -            | -            | PORT_WKUP_IN10 |

|    | PC12 | -            | -            | -            | PORT_WKUP_IN11 |

|    | PC13 | -            | -            | -            | PORT_WKUP_IN0  |

|    | PC14 | TMR2_PWM_OUT | TMR1_PWM_OUT | -            | PORT_WKUP_IN1  |

|    | PC15 | -            | TMR0_PWM_OUT | -            | PORT_WKUP_IN2  |

| PD | PD0  | -            | -            | -            | PORT_WKUP_IN3  |

|    | PD1  | -            | -            | -            | PORT_WKUP_IN4  |

|    | PD2  | TMR2_PWM_OUT | TMR1_PWM_OUT | -            | PORT_WKUP_IN5  |

|    | PD3  | -            | TMR0_PWM_OUT | -            | PORT_WKUP_IN6  |

|    | PD4  | -            | TMR5_PWM_OUT | -            | PORT_WKUP_IN7  |

|    | PD5  | -            | TMR3_PWM_OUT | -            | PORT_WKUP_IN8  |

| PE | PE0  | SPI0_NSS     | TMR4_PWM_OUT | -            | PORT_WKUP_IN7  |

|    | PE1  | SPI0_IO3     | -            | -            | PORT_WKUP_IN6  |

|    | PE2  | TMR2_CAP_PIN | TMR2_INC_PIN | RTCC_TRGIO   | PORT_WKUP_IN8  |

注：UART0\_RX 单线通信时作收发引脚，双线工作时作接收引脚。

## 4 系统及存储器架构

JS32L010 芯片采用了哈佛结构，具有低中断延迟时间和高集成度特性，而且非常适合于那些需要高性能和低功耗微控制器的市场领域。预先定义的存储器映射和高达 4 GB 的存储空间，充分保证了系统的灵活性和可扩展性。

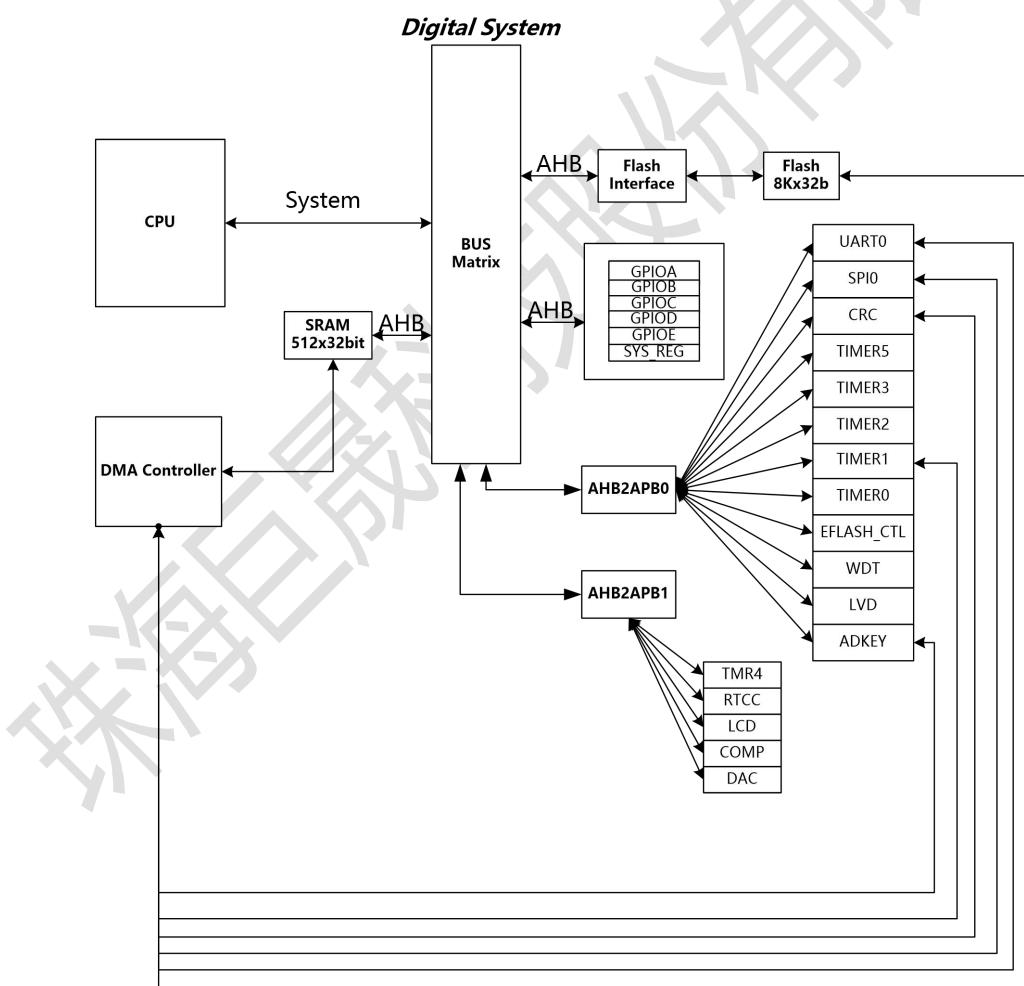

### 4.1 系统架构

JS32L010 芯片采用 32 位多层次总线结构，该结构可使系统中的多个主机和从机之间的并行通信成为可能。多层次总线结构包括一个 AHB 互联矩阵、两个 AHB 总线和两个 APB 总线。AHB 互联矩阵的互联关系将在下面进行说明。

JS32L010 主系统由以下两部分构成：

- 2 个驱动单元：

- CPU 内核系统总线(S-bus)

- DMA 总线

- 2 个存储单元

- 内部闪存存储器

- 内部 SRAM

图 4-1 JS32L010 总线系统架构图

#### 系统总线

此总线连接 CPU 内核的系统总线(外设总线)到总线矩阵，总线矩阵协调着内核和各个高速部件间的访问。

#### DMA 控制器

此总线将 CPU 与各外设模块访问相联竞争，协调访问优先级，仲裁等。

表 4-1 DMA 优先级

| 模块     | 优先级 | 备注   |

|--------|-----|------|

| CPU    | 0   | ↑ 最高 |

| SPI0   | 1   |      |

| UART0  | 2   |      |

| ADKEY  | 3   |      |

| CRC    | 4   |      |

| TIMER1 | 5   |      |

| FLASH  | 6   | 最低   |

### 总线矩阵(Bus Matrix)

- 总线矩阵管理着内核系统总线与各外设模块的访问仲裁，总线矩阵由主模块总线及从模块总线组成。

- AHB 外设通过总线矩阵与系统总线相连。

- AHB 到 APB 桥(AHB2APB bridges-APB)。

- AHB 到 APB 桥在 AHB 与 APB 总线间提供同步连接。

注：当对 APB 寄存器进行 8 位或者 16 位访问时，该访问会被自动转换成 32 位的访问：桥会自动将 16 位或者 8 位的数据扩展以配合 32 位的宽度。

## 4.2 存储器映射

此 32 位处理器采用同一套总线来读取指令和加载/存储数据。指令代码和数据都位于相同的存储器地址空间，但在不同的地址范围。程序存储器，数据存储器，寄存器和 I/O 端口都在同一个线性的 4 GB 的地址空间之内。这是 32 位处理器的最大地址范围，因为它的地址总线宽度是 32 位。此外，为了降低不同客户在相同应用时的软件复杂度，存储映射是按 32 位处理器提供的规则预先定义的。在存储器映射表中，一部分地址空间由 32 位处理器的系统外设所占用，且不可更改。此外，其余部分地址空间可由芯片供应商定义使用。JS32L010 芯片的存储器映射表显示了 JS32L010 芯片的存储器映射，包括代码、SRAM、外设和其他预先定义的区域。简化了每个外设的地址译码。

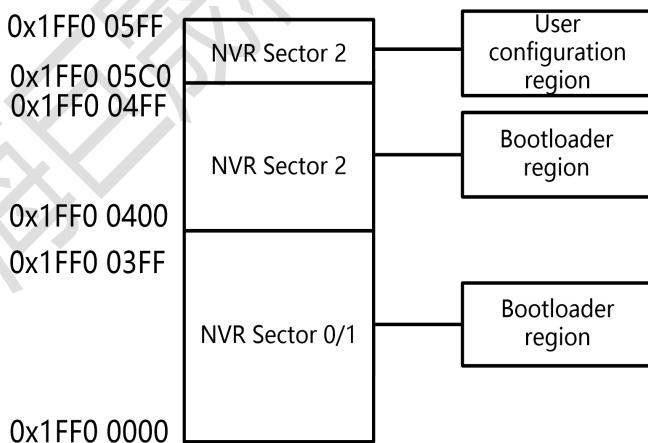

图 4-2 Flash NVR 区域定义

| System memory mapping |                     | IO device space mapping |               |

|-----------------------|---------------------|-------------------------|---------------|

| 0x5FFF FFFF           | IO device           | 0x5FFF FFFF             | Reserved      |

| 0x4000 0000           |                     | 0x4002 1000             | Reserved      |

| 0x3FFF FFFF           |                     | 0x4002 0FFF             | GPIOA/B/C/D/E |

|                       |                     | 0x4002 0B00             | SYS_REG       |

|                       |                     | 0x4002 0A0F             | LCD           |

|                       |                     | 0x4002 0000             | DAC           |

|                       |                     | 0x4001 04FF             | COMP          |

|                       |                     | 0x4001 0400             | TIMER4        |

|                       |                     | 0x4001 03FF             | RTCC          |

|                       |                     | 0x4001 0220             | TIMER4        |

|                       |                     | 0x4001 021F             | SPI0/IIC0     |

|                       |                     | 0x4001 0200             | UART0         |

|                       |                     | 0x4001 01FF             | EFLASH        |

|                       |                     | 0x4001 0100             | CRC           |

|                       |                     | 0x4001 00FF             | TIMER5        |

|                       |                     | 0x4001 0130             | TIMER3        |

|                       |                     | 0x4001 012F             | TIMER2        |

|                       |                     | 0x4001 0100             | TIMER1_DMA    |

|                       |                     | 0x4000 44FF             | TIMER1        |

|                       |                     | 0x4000 4400             | TIMERO        |

|                       |                     | 0x4000 40FF             | WDT           |

|                       |                     | 0x4000 4000             | PLLFRAC       |

|                       |                     | 0x4000 3FFF             | ADKEY         |

|                       |                     | 0x4000 3000             | LVD           |

|                       |                     | 0x4000 2FFF             |               |

|                       |                     | 0x4000 2000             |               |

|                       |                     | 0x4000 16FF             |               |

|                       |                     | 0x4000 1600             |               |

|                       |                     | 0x4000 14FF             |               |

|                       |                     | 0x4000 1400             |               |

|                       |                     | 0x4000 13FF             |               |

|                       |                     | 0x4000 1300             |               |

|                       |                     | 0x4000 12FF             |               |

| 0x2000 0800           | SRAM<br>(2KByte)    | 0x40001228              |               |

| 0x2000 07FF           |                     | 0x4000 1227             |               |

| 0x2000 0000           | Reserved            | 0x4000 1200             |               |

| 0x1FFF FFFF           |                     | 0x4000 11FF             |               |

| 0x1FF0 0600           | NVR                 | 0x4000 1100             |               |

| 0x1FF0 05FF           |                     | 0x4000 10FF             |               |

| 0x1FF0 0000           | Reserved            | 0x4000 1000             |               |

| 0x0000 8000           | eFlash<br>(32KByte) | 0x4000 03FF             |               |

| 0x0000 7FFF           |                     | 0x4000 0300             |               |

| 0x0000 0000           |                     | 0x4000 02FF             |               |

图 4-3 JS32L010 存储器映射表

#### 4.2.1 片上 SRAM

芯片内置 2K 字节的 SRAM。它可以按字节(8 位)、半字(16 位)或字(32 位)进行访问。SRAM 起始地址为 0x2000 0000。可以被 CPU 或者 DMA 用最快的系统时钟且不插入任何等待进行访问。

注：DMA 支持访问有 EFLASH, UART, SPI, CRC, ADC, TIMER1。

#### 4.2.2 片上 FLASH 概述

闪存存储器有两个不同存储区域：

- 主闪存存储块，它包括应用程序和用户数据区(若需要时)

- 信息块，其包含两个部分：

- 选项字节(Option bytes) - 内含硬件及存储保护用户配置选项。

- 系统存储器(System memory) - 其包含 Boot loader 代码。详细参见内置闪存存储器章节。

- 闪存接口基于 AHB 协议执行指令和数据存取。其预取缓冲的功能可加速 CPU 执行代码的速度。

#### 4.2.3 引导配置

芯片复位后，通过客户自己在副闪存的配置，选择启动模式引脚是 PC9 还是 PA3，默认工作是上拉还是下拉。正常启动后，CPU 从地址 0x0000 0000 获取堆栈顶的地址，并从存储器的 0x0000 0004 位置指示的地址开始执行代码。

Boot loader 程序存放在副闪存中，由用户根据实际情况自行决定是否写入使用。若已写入 Boot loader 程序，可以通过 UART 对 Boot loader 程序或者用户程序进行升级。

珠海巨晟科技股份有限公司

## 5 嵌入式闪存 (FLASH)

### 5.1 闪存主要特性

- 高达 32K 字节闪存存储器

- 存储器结构：

- 主闪存空间：32K 字节

- 副闪存空间：1.5K 字节

- 带预取缓冲器的读接口

- 闪存编程和擦除操作

- 访问和写保护

- 低功耗模式

### 5.2 闪存功能描述

#### 5.2.1 闪存结构

闪存空间由 32 位宽的存储单元组成，既可以存代码又可以存数据。主闪存块按 32 页（每页 1K 字节）分块，以页为单位设置写保护（参见存储保护相关内容）。

表 5-1 闪存结构

| 模块      | 名称            | 地址                        | 大小(字节) |

|---------|---------------|---------------------------|--------|

| 主闪存空间   | Page 0        | 0x0000 0000 – 0x0000 03FF | 1K     |

|         | Page 1        | 0x0000 0400 – 0x0000 07FF | 1K     |

|         | Page 2        | 0x0000 0800 – 0x0000 0BFF | 1K     |

|         | Page 3        | 0x0000 0C00 – 0x0000 0FFF | 1K     |

|         | ...           | ...                       | 1K     |

|         | Page 30       | 0x0000 7800 – 0x0000 7BFF | 1K     |

|         | Page 31       | 0x0000 7C00 – 0x0000 7FFF | 1K     |

| 副闪存空间   | Sector 0      | 0x1FF0 0000 – 0x1FF0 01FF | 512    |

|         | Sector 1      | 0x1FF0 0200 – 0x1FF0 03FF | 512    |

|         | Sector 2      | 0x1FF0 0400 – 0x1FF0 05FF | 512    |

| 闪存寄存器接口 | CTRLR0        | 0x4000 3000 – 0x4000 3003 | 4      |

|         | KST           | 0x4000 3004 – 0x4000 3007 | 4      |

|         | DONE          | 0x4000 3008 – 0x4000 300B | 4      |

|         | PROG_ADDR     | 0x4000 3010 – 0x4000 3013 | 4      |

|         | PROG_DATA     | 0x4000 3018 – 0x4000 301B | 4      |

|         | ERASE_CTRL    | 0x4000 3020 – 0x4000 3023 | 4      |

|         | TIME_REG0     | 0x4000 3030 – 0x4000 3033 | 4      |

|         | TIME_REG1     | 0x4000 3034 – 0x4000 3037 | 4      |

|         | NVR_PASSWORD  | 0x4000 3050 – 0x4000 3053 | 4      |

|         | MAIN_PASSWORD | 0x4000 3054 – 0x4000 3057 | 4      |

|         | CRC_ADDR      | 0x4000 3058 – 0x4000 305B | 4      |

|         | CRC_LEN       | 0x4000 305C – 0x4000 305F | 4      |

|         | CRC_OUT       | 0x4000 3060 – 0x4000 3063 | 4      |

|         | MODE          | 0x4000 3070 – 0x4000 3073 | 4      |

|         | STA1          | 0x4000 3074 – 0x4000 3077 | 4      |

|         | STA2          | 0x4000 3078 – 0x4000 307B | 4      |

|         | CFG_SECTOR    | 0x4000 307C – 0x4000 307F | 4      |

### 5.2.2 闪存读保护

读操作在整个芯片工作电压范围内都可以完成，用于存放指令或者数据，若工作频率提升到 30MHz 以上，需要让 Flash 的读时序执行分频。

芯片带有缓冲区和预取缓冲区，提升 Flash 的访问效率。

当用户配置区经过自定义的保护配置后，若 UART 单线升级或 SWD 接口连接上时，会自动对 Flash 执行保护机制。

### 5.2.3 闪存烧写和擦除操作

烧写和擦除操作在整个芯片工作电压范围内都可以完成。

烧写和擦除操作由下列 6 个寄存器完成，先根据烧写的时钟配置好烧写时序(TIME\_REG0)，再配置烧写密码，配置好编程地址，最后配置好编程数据，即可开始执行烧写，然后等待操作结束。

- 时序 0 寄存器 ( TIME\_REG0 )

- 密码 0 寄存器 ( NVR\_PASSWORD )

- 密码 1 寄存器 ( MAIN\_PASSWORD )

- 编程地址寄存器 ( PROG\_ADDR )

- 编程数据寄存器 ( PROG\_DATA )

- 状态寄存器 ( DONE )

### 5.2.4 闪存寄存器接口

#### 5.2.4.1 配置寄存器 (CTRLR0)

Address offset: 0x00

| Width | Name             | Reset | Property | Description                                                                                                          |

|-------|------------------|-------|----------|----------------------------------------------------------------------------------------------------------------------|

| 31:17 | Reserved         | -     | -        | -                                                                                                                    |

| 16    | PRO_CLK_SET      | 1'b0  | RW       | FLASH 烧写时钟源选择，推荐使用 RC 时钟<br>0: 高速 RC 时钟 2 分频<br>1: 晶振，若 RC 不准时才使用                                                    |

| 15:12 | Reserved         | -     | -        | -                                                                                                                    |

| 11    | LVD_PRO_EN       | 1'b0  | RW       | 在 LVD 断电时，是否允许打断 FLASH 编程和擦除，一般在断电时，立刻把重要数据保存在 FLASH 上，就打开此功能，用于快速让 FLASH 处于空闲状态<br>0: 不允许<br>1: 允许                  |

| 10    | PRO_RAM_MODE_SET | 1'b0  | RW       | 直接把 RAM 的数据写到 FLASH，并在 FLASH 最后自动添加 CRC 校验值，具体影响到几个寄存器 PROG_ADDR、CRC_ADDR、CRC_LEN<br>0: CRC 模式<br>1: RAM TO FLASH 模式 |

| 9     | READM1           | 1'b0  | RW       | FLASH 测试使用，正常情况下配置成 0                                                                                                |

| 8     | READM0           | 1'b0  | RW       | FLASH 测试使用，正常情况下配置成 0                                                                                                |

| 7     | SRAM_DIR_OUT_EN  | 1'b0  | RW       | FLASH 的数据直接输出，用于系统时钟低频时，且 CACHE_EN 和 PREFETCH_EN 都不使能时使用<br>0: 不使能<br>1: 使能                                          |

| 6     | Reserved         | -     | -        | -                                                                                                                    |

| 5     | Reserved         | -     | -        | -                                                                                                                    |

|   |               |      |    |                                        |

|---|---------------|------|----|----------------------------------------|

| 4 | WRITE_BACK_EN | 1'b1 | RW | 编程/扇区擦除 自动回写到 CACHE<br>0: 不使能<br>1: 使能 |

| 3 | Reserved      | -    | -  | -                                      |

| 2 | PREFETCH_EN   | 1'b0 | RW | 预取使能位<br>0: 不使能<br>1: 使能               |

| 1 | Reserved      | -    | -  | -                                      |

| 0 | CACHE_EN      | 1'b0 | RW | CACHE 使能位<br>0: 不使能<br>1: 使能           |

#### 5.2.4.2 触发寄存器 (KST)

Address offset: 0x04

| Width | Name            | Reset | Property | Description                        |

|-------|-----------------|-------|----------|------------------------------------|

| 31:27 | Reserved        | -     | -        | -                                  |

| 26    | CRC_KICK_EN     | 1'b0  | WO       | FLASH CRC 校验使能<br>0: 不使能<br>1: 使能  |

| 25:21 | Reserved        | -     | -        | -                                  |

| 20    | CACHE_CLR_EN    | 1'b0  | WO       | CACHE 清除使能<br>0: 不使能<br>1: 使能      |

| 19:11 | Reserved        | -     | -        | -                                  |

| 10    | CRC_START       | 1'b0  | WO       | FLASH CRC Check, 和第 26 位同时写 '1' 触发 |

| 9:5   | Reserved        | -     | -        | -                                  |

| 4     | CACHE_CLR_START | 1'b0  | WO       | CACHE 开始清除, 和第 20 位同时写 '1' 触发      |

| 3:0   | Reserved        | -     | -        | -                                  |

#### 5.2.4.3 状态寄存器 (DONE)

Address offset: 0x08

| Width | Name           | Reset | Property | Description                 |

|-------|----------------|-------|----------|-----------------------------|

| 31:13 | Reserved       | -     | -        | -                           |

| 12    | ERASE_OK_FLAG  | 1'b1  | RO       | 0: 擦除失败<br>1: 擦除成功          |

| 11    | PRO_OK_FLAG    | 1'b1  | RO       | 0: 烧写失败<br>1: 烧写成功          |

| 10    | CRC_DONE       | 1'b1  | RO       | 0: 进行中<br>1: 空闲状态           |

| 9:7   | Reserved       | -     | -        | -                           |

| 6     | PRO_DONE       | 1'b1  | RO       | 编程结束标志<br>0: 进行中<br>1: 空闲状态 |

| 5     | Reserved       | -     | -        | -                           |

| 4     | CACHE_CLR_FLAG | 1'b1  | RO       | CACHE 清除标志<br>0: 进行中        |

|     |                   |      |    |                                        |

|-----|-------------------|------|----|----------------------------------------|

|     |                   |      |    | 1: 空闲状态                                |

| 3:2 | Reserved          | -    | -  | -                                      |

| 1   | MAIN_ERASE_FLAG   | 1'b1 | RO | MAIN 区域全擦除标志<br>0: 正在运行<br>1: 空闲状态     |

| 0   | SECTOR_ERASE_FLAG | 1'b1 | RO | 扇区(512 BYTE)擦除标志<br>0: 正在运行<br>1: 空闲状态 |

#### 5.2.4.4 编程地址寄存器 (PROG\_ADDR)

Address offset: 0x10

| Width | Name        | Reset | Property | Description                                                                                    |

|-------|-------------|-------|----------|------------------------------------------------------------------------------------------------|

| 31:30 | PRO_BYT_SET | 2'b10 | RW       | 一次编程的 BYTE 位选择<br>b00: PROG_DATA[7:0]被编程<br>b01: PROG_DATA[15:0]被编程<br>b10: PROG_DATA[31:0]被编程 |

| 29    | PRO_NVR_SET | 1'b0  | RW       | 编程的地址是否 NVR 区域<br>0: MAIN 区域<br>1: NVR 区域                                                      |

| 28:2  | PRO_ADDR    | 27'h0 | RW       | FLASH 编程的地址, 以 4 字节为单位进行编程<br>NOTE: 在配置寄存器里的第 10 位有效时, 此寄存器作为 FLASH 编程的开始地址                    |

| 1:0   | PRO_ADDR_L  | 2'b0  | RO       | 低 2 位地址固定为 0, 4 字节对齐                                                                           |

#### 5.2.4.5 编程数据寄存器 (PROG\_DATA)

Address offset: 0x18

| Width | Name     | Reset | Property | Description                                                             |

|-------|----------|-------|----------|-------------------------------------------------------------------------|

| 31:0  | PRO_DATA | 32'h0 | RW       | FLASH 编程的数据, 需要配置好地址才可进行<br>NOTE: 在配置寄存器里的第 10 位有效时, 此寄存器作为 FLASH 编程的数据 |

#### 5.2.4.6 擦除控制寄存器 (ERASE\_CTRL)

Address offset: 0x20

| Width | Name               | Reset | Property | Description                                 |

|-------|--------------------|-------|----------|---------------------------------------------|

| 31    | CHIP_ERASE_START   | 1'b0  | RO       | CHIP 全擦除的触发, 写 “1” 触发, 需要先配置密码              |

| 30    | SECTOR_ERASE_START | 1'b0  | RO       | SECTOR 擦除的触发, 写 “1” 触发, 需要先配置密码             |

| 29    | NVR_SECTOR_EN      | 1'b0  | RW       | NVR 的 SECTOR 使能位<br>0: MAIN 区域<br>1: NVR 区域 |

| 28:7  | Reserved           | -     | -        | -                                           |

| 6:0   | ERASE_SECTOR_ADDR  | 7'h0  | RW       | 擦除的 SECTOR 选择, 范围 0-127                     |

#### 5.2.4.7 时序 0 寄存器 (TIME\_REG0)

Address offset: 0x30

| Width | Name     | Reset   | Property | Description                  |

|-------|----------|---------|----------|------------------------------|

| 31:20 | Reserved | -       | -        | -                            |

| 19:16 | PGH      | 4'b0001 | RW       | WEB 低 到 PROG2 高 保持时间最小为 15ns |

| 15:12 | ADS      | 4'b0001 | RW       | 字节/地址/数据设置的最小时间是 15ns        |

| 11:8  | ADH      | 4'b0001 | RW       | 字节/地址/数据保持时间最小为 15ns         |

| 7:4   | RW       | 4'b1000 | RW       | 编程/擦除后的下一个操作的延迟时间为 100ns     |

| 3:0   | RC       | 1'b0    | RW       | 读取周期最小时间为 25/30ns            |

#### 5.2.4.8 时序 1 寄存器 (TIME\_REG1)

Address offset: 0x34

| Width | Name        | Reset   | Property | Description                    |

|-------|-------------|---------|----------|--------------------------------|

| 31:20 | Reserved    | -       | -        | -                              |

| 18:8  | 1MS_CNT_SET | 11'h3E8 | RO       | 1ms 的时间配置值, 以 1us 为单位          |

| 7:0   | 1US_CNT_SET | 8'h0D   | RW       | 1us 的时间配置值, 系统默认是 26MHz 的 2 分频 |

#### 5.2.4.9 密码 1 寄存器 (MAIN\_PASSWORD)

Address offset: 0x54

| Width | Name           | Reset | Property | Description                               |

|-------|----------------|-------|----------|-------------------------------------------|

| 31:10 | MAIN_PASS_WORD | 32'h0 | RW       | 密码为 0x20170230, 只有打开密码后, 才能对 MAIN 进行擦除和编程 |

#### 5.2.4.10 密码 0 寄存器 (NVR\_PASSWORD)

Address offset: 0x50

| Width | Name          | Reset | Property | Description                              |

|-------|---------------|-------|----------|------------------------------------------|

| 31:10 | NVR_PASS_WORD | 32'h0 | RW       | 密码为 0x20150931, 只有打开密码后, 才能对 NVR 进行擦除和编程 |

#### 5.2.4.11 CRC 地址配置寄存器 (CRC\_ADDR)

Address offset: 0x58

| Width | Name     | Reset | Property | Description                                                                           |

|-------|----------|-------|----------|---------------------------------------------------------------------------------------|

| 31:30 | Reserved | -     | -        | -                                                                                     |

| 29    | NVR_SET  | 1'b0  | RW       | 地址是否 NVR 区域<br>0: MAIN 区域<br>1: NVR 区域                                                |

| 28:2  | DMA_ADDR | 27'h0 | RW       | CRC DMA 的开始地址, 只指向 EFLASH, 且是物理地址(4 字节对齐)<br>NOTE: 在配置寄存器里的第 10 位有效时, 此寄存器配置成 RAM 的地址 |

| 1:0   | Reserved | -     | -        | -                                                                                     |

#### 5.2.4.12 CRC 长度配置寄存器 (CRC\_LEN)

Address offset: 0x5C

| Width | Name    | Reset | Property | Description                                        |

|-------|---------|-------|----------|----------------------------------------------------|

| 31:0  | DMA_LEN | 32'h0 | RW       | CRC 长度<br>Note: 在配置寄存器里的第 10 位有效时, 此寄存器配置成 RAM 的长度 |

#### 5.2.4.13 CRC 结果寄存器 (CRC\_OUT)

Address offset: 0x60

| Width | Name    | Reset | Property | Description                                                                                                                              |

|-------|---------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0  | CRC_OUT | 32'h0 | RO       | CRC 的结果, 多项式 CRC-32 如下:<br>$x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$ |

#### 5.2.4.14 模式寄存器(MODE)

Address offset: 0x70

| Width | Name        | Reset | Property | Description                               |

|-------|-------------|-------|----------|-------------------------------------------|

| 31:19 | Reserved    | -     | -        | -                                         |

| 18    | DEBUG_MODE  | 1'b0  | RO       | FLASH 进入程序 DEBUG 模式标志位<br>0: 无效<br>1: 有效  |

| 17    | UPDATE_MODE | 1'b0  | RO       | FLASH 进入程序单 PIN 升级模式标志位<br>0: 无效<br>1: 有效 |

| 16    | TEST_MODE   | 1'b0  | RO       | EFLASH 进入出厂 TEST 模式标志位<br>0: 无效<br>1: 有效  |

| 15:4  | Reserved    | -     | -        | -                                         |

| 3     | PROTC0_MODE | 1'b0  | RO       | FLASH 进入全被保护模式标志位<br>0: 无效<br>1: 有效       |

| 2     | ALL_MODE    | 1'b0  | RO       | FLASH 进入自由模式标志位<br>0: 无效<br>1: 有效         |

| 1     | SUPER_MODE  | 1'b0  | RO       | FLASH 进入超级模式标志位<br>0: 无效<br>1: 有效         |

| 0     | Reserved    | -     | -        | -                                         |

#### 5.2.4.15 状态寄存器 1(STA1)

Address offset: 0x74

| Width | Name            | Reset | Property | Description                                      |

|-------|-----------------|-------|----------|--------------------------------------------------|

| 31    | MAIN_FALID_FLAG | 1'b0  | RO       | FLASH MAIN 区域 CODE CRC 校验出错标志位<br>0: 正确<br>1: 错误 |

| 30    | BOOT_FALID_FLAG | 1'b0  | RO       | FLASH 有 Bootloader 的区域 CRC 校验出错标志位               |

|       |                         |      |    |                                                                          |

|-------|-------------------------|------|----|--------------------------------------------------------------------------|

|       |                         |      |    | 志位<br>0: 正确<br>1: 错误                                                     |

| 29    | MAIN_EPMTRY_FLAG        | 1'b1 | RO | FLASH MAIN 区域 CODE 全空标志位<br>0: 非空<br>1: 全空                               |

| 28    | EFLASH_ALL_OK_FLAG      | 1'b1 | RO | FLASH 所有的 SECTOR 都是好片标志位<br>0: 有坏片<br>1: 全是好片                            |

| 27:23 | Reserved                | -    | -  | -                                                                        |

| 22    | BOOT_USR_CFG_VALID_FLAG | 1'b0 | RO | FLASH Bootloader+用户配置拷贝有效标志位<br>0: 无效<br>1: 有效                           |

| 21    | BOOT_USR_CFG_DIR_FLAG   | 1'b0 | RO | FLASH Bootloader+用户配置拷贝方向标志位<br>0: NVR 区更新到 MAIN 区<br>1: MAIN 区更新到 NVR 区 |

| 20    | BOOT_USR_CFG_OK_FLAG    | 1'b0 | RO | FLASH Bootloader+用户配置拷贝后 CRC 校验正确标志位<br>0: 错误<br>1: 正确                   |

| 19    | MAIN_BOOT_EMPTY_FLAG    | 1'b1 | RO | FLASH Main 区 Bootloader 全空标志位<br>0: 非空<br>1: 全空                          |

| 18    | MAIN_BOOT_OK_FLAG       | 1'b0 | RO | FLASH MAIN 区 BootloaderCRC 校验正确标志位<br>0: 错误<br>1: 正确                     |

| 17    | MAIN_USER_EMPTY_FLAG    | 1'b0 | RO | FLASH MAIN 区用户配置区全空标志位<br>0: 非空<br>1: 全空                                 |

| 16    | MAIN_USER_OK_FLAG       | 1'b0 | RO | FLASH MAIN 区用户配置 CRC 校验正确标志位<br>0: 错误<br>1: 正确                           |

| 15    | NVR_BOOT_EMPTY_FLAG     | 1'b1 | RO | FLASH NVR 区 Bootloader 全空标志位<br>0: 非空<br>1: 全空                           |

| 14    | NVR_BOOT_OK_FLAG        | 1'b0 | RO | FLASH NVR 区 Bootloader CRC 校验正确标志位<br>0: 错误<br>1: 正确                     |

| 13    | NVR_USER_EMPTY_FLAG     | 1'b0 | RO | FLASH NVR 区用户配置区全空标志位<br>0: 非空<br>1: 全空                                  |

| 12    | NVR_USER_OK_FLAG        | 1'b0 | RO | FLASH NVR 区用户配置 CRC 校验正确标志位<br>0: 错误<br>1: 正确                            |

| 11:0  | Reserved                | -    | -  | -                                                                        |

### 5.2.4.16 状态寄存器 2(STA2)

Address offset: 0x78

| Width | Name               | Reset | Property | Description                                                            |

|-------|--------------------|-------|----------|------------------------------------------------------------------------|

| 31:20 | Reserved           | -     | -        | -                                                                      |

| 19:17 | Reserved           | -     | -        | -                                                                      |

| 16    | CHIP_ERASE_OK_FLAG | 1'b0  | RO       | FLASH CHIP 擦写成功标志位<br>0: 擦写失败<br>1: 擦写成功                               |

| 15:12 | Reserved           | -     | -        | -                                                                      |

| 11:8  | Reserved           | -     | -        | -                                                                      |

| 7:6   | Reserved           | -     | -        | -                                                                      |

| 5     | Reserved           | -     | -        | -                                                                      |

| 4     | RC_CLK_SEL         | 1'b0  | RO       | RC 启动时钟选择位<br>0: RC 启动时钟为 128KHz 频率<br>1: RC 启动时钟为 HROSC 的 2 分频(13MHz) |

| 3     | Reserved           | -     | -        | -                                                                      |

| 2     | MAIN_CRC_EN        | 1'b1  | RO       | MAIN 区 CRC 校验使能位<br>0: 不使能<br>1: 使能                                    |

| 1     | BOOT_BKP_EN        | 1'b0  | RO       | Bootloader 备份使能位<br>0: 不使能<br>1: 使能                                    |

| 0     | SCRAMBLE_EN        | 1'b1  | RO       | EFLASH 加扰有效位标志位<br>0: 无效<br>1: 有效                                      |

### 5.2.4.17 主扇区信息寄存器 (CFG\_SECTOR)

Address offset: 0x7C

| Width | Name       | Reset  | Property | Description |

|-------|------------|--------|----------|-------------|

| 31:00 | SECTOR_NUM | 32'h40 | RO       | 主程序区最大扇区个数  |

## 5.2.5 NVR2 闪存用户配置区

### 5.2.5.1 配置 0 (0x1FF0 05C0)

| Width | Name             | Reset | Property | Description                                    |

|-------|------------------|-------|----------|------------------------------------------------|

| 31:11 | Reserved         | -     | -        | -                                              |

| 10    | CODE_PROTECT_DIS | 1'b1  | RO       | 代码保护使能位<br>0: 保护<br>1: 不保护                     |

| 9     | BOOT_EN          | 1'b1  | RO       | BOOTLOADER 使能位<br>0: 使能<br>1: 不使能              |

| 8     | NVR_BACKUP_EN    | 1'b1  | RO       | NVR0/1/2 区域是否需要备份到 MAIN 区域中<br>0: 备份<br>1: 不备份 |

| 7:2   | Reserved         | -     | -        | -                                              |

|     |               |       |    |                          |

|-----|---------------|-------|----|--------------------------|

| 1:0 | NVR_WRITE_PER | 2'b11 | RO | NVR 的写权限, 每一位代表一个 SECTOR |

|-----|---------------|-------|----|--------------------------|

### 5.2.5.2 配置 1 (0x1FF0 05C4)

| Width | Name           | Reset       | Property | Description                                             |

|-------|----------------|-------------|----------|---------------------------------------------------------|

| 31:0  | MAIN_WRITE_PER | 32'hFFFFFFF | RO       | MAIN 的写权限, 根据 FLASH 的存储空间大小确定每一位控制多少字节<br>每一位代表 1K BYTE |

### 5.2.5.3 配置 2 (0x1FF0 05D4)

| Width | Name             | Reset    | Property | Description                                              |

|-------|------------------|----------|----------|----------------------------------------------------------|

| 31    | MAIN_CODE_CRC_EN | 1'b1     | RO       | MAIN 区域程序 CRC 检验的使能位<br>0: 关闭<br>1: 打开                   |

| 30:16 | Reserved         | -        | -        | -                                                        |

| 15:0  | MAIN_CODE_LEN    | 16'hFFFF | RO       | MAIN 区域程序的长度, 4 字节为单元。<br>MAIN 区域除去该程序区域后, 剩下的为 DATA 区域。 |

### 5.2.5.4 配置 3 (0x1FF0 05E0)

| Width | Name            | Reset | Property | Description                                                                                                                                                                                                             |

|-------|-----------------|-------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:15 | Reserved        | -     | -        | -                                                                                                                                                                                                                       |

| 14    | SWD_EN          | 1'b1  | RO       | SWD 接口是否有效<br>0: 不使能<br>1: 使能                                                                                                                                                                                           |

| 13    | Reserved        | -     | -        | -                                                                                                                                                                                                                       |

| 12    | MCLR_EN         | 1'b1  | RO       | MCLR 使能位<br>0: 不使能<br>1: 使能                                                                                                                                                                                             |

| 11    | Reserved        | -     | -        | -                                                                                                                                                                                                                       |

| 10:9  | SWD_PULL_MODE   | 1'b11 | RO       | SWD 复位上拉或下拉, 根据此位来确定默认为复位上拉或下拉<br>b10: 下拉<br>b11: 上拉<br>其它: 没有上下拉 (SWD 无效)                                                                                                                                              |

| 8     | Reserved        | -     | -        | -                                                                                                                                                                                                                       |

| 7:6   | Reserved        | -     | -        | -                                                                                                                                                                                                                       |

| 5:0   | UART_UPDATE_MAP | 6'h3F | RO       | UART Port 单线升级映射<br>h00~h01: 分别对应 PA0~PA1<br>h04~h0F: 分别对应 PA4~PA15<br>h10~h1F: 分别对应 PB0~PB15<br>h20~h27: 分别对应 PC0~PC7<br>h2A: 对应 PE1<br>h2B: 对应 PE0<br>h2C: 对应 PE2<br>h2D~h32: 分别对应 PC10~PC15<br>h33~h38: 分别对应 PD0~PD5 |

|  |  |  |  |                   |

|--|--|--|--|-------------------|

|  |  |  |  | hFF: 无效<br>其它: 禁止 |

|--|--|--|--|-------------------|

## 5.2.6 NVR3 闪存芯片信息区

### 5.2.6.1 芯片信息 0(0x1FF0 0600)

| Width | Name | Reset         | Property | Description |

|-------|------|---------------|----------|-------------|

| 31:0  | UID0 | 32'hFFFFFFFFF | RO       | UID 信息 0    |

### 5.2.6.2 芯片信息 0(0x1FF0 0604)

| Width | Name | Reset         | Property | Description |

|-------|------|---------------|----------|-------------|

| 31:0  | UID1 | 32'hFFFFFFFFF | RO       | UID 信息 1    |

### 5.2.6.3 芯片信息 0(0x1FF0 0608)

| Width | Name | Reset         | Property | Description |

|-------|------|---------------|----------|-------------|

| 31:0  | UID2 | 32'hFFFFFFFFF | RO       | UID 信息 2    |

### 5.2.6.4 芯片信息 0(0x1FF0 0618)

| Width | Name        | Reset | Property | Description |

|-------|-------------|-------|----------|-------------|

| 31:0  | CUSTOMER ID | 32'b0 | RO       | 客户信息        |

## 6 中断和事件(INT/EVT)

### 6.1 嵌套向量中断控制器

- 特征

- 中断都可屏蔽(除了 NMI)

- 4 个可编程的优先等级

- 低延迟的异常和中断处理

- 电源管理控制

#### 系统控制寄存器的实现

嵌套向量中断控制器(NVIC)和处理器核的接口紧密相连，可以实现低延迟的中断处理和高效地处理晚到的中断。

嵌套向量中断控制器管理着包括核异常等中断。关于更多的异常和 NVIC 编程的说明请参考 CPU 技术参考手册。

### 6.2 系统滴答(SysTick)校准值寄存器

本芯片支持系统滴答计时。

### 6.3 中断功能描述

处理器和嵌套式矢量型中断控制器(NVIC)在处理(Handler)模式下对所有异常进行优先级区分以及处理。当异常发生时，系统会自动将当前处理器工作状态压栈，在执行完中断服务子程序 (ISR)后自动将其出栈。

取向量是和当前工作态压栈并行进行的，从而提高了中断入口效率。处理器支持咬尾中断，可实现背靠背中断，大大削减了反复切换工作态所带来的负荷。

表 6-1 NVIC 异常类型

| 异常类型            | 向量编号  | 优先级     | 向量地址                        | 描述                |

|-----------------|-------|---------|-----------------------------|-------------------|

| -               | 0     | --      | 0x0000 0000                 | Reserved          |

| 复位              | 1     | -3 (最高) | 0x0000 0004                 | 复位                |

| NMI             | 2     | -2      | 0x0000 0008                 | 不可屏蔽中断            |

| 硬件故障(HardFault) | 3     | -1      | 0x0000 000C                 | 各种硬件级别故障          |

| -               | 4-10  | --      | 0x0000 0010-<br>0x0000 002B | Reserved          |

| SVcall 服务调用     | 11    | --      | 0x0000 002C                 | 通过 SWI 指令实现系统服务调用 |

| -               | 12-13 | --      | 0x0000 0030-<br>0x0000 0037 | Reserved          |

| PendSV 挂起服务     | 14    | 可编程设置   | 0x0000 0038                 | 可挂起的系统服务请求        |

| 系统节拍            | 15    | 可编程设置   | 0x0000 003C                 | 系统节拍定时器           |

表 6-2 中断向量表

| 中断编号 | 向量编号 | 外设中断描述     | 向量地址        |

|------|------|------------|-------------|

| IRQ0 | 16   | LVD IRQn   | 0x0000 0040 |

| IRQ1 | 17   | UART0 IRQn | 0x0000 0044 |

| IRQ2 | 18   | SPI0 IRQn  | 0x0000 0048 |

| IRQ3 | 19   | GPIOA IRQn | 0x0000 004C |

| IRQ4 | 20   | GPIOB IRQn | 0x0000 0050 |

| IRQ5 | 21   | GPIOC IRQn | 0x0000 0054 |

| IRQ6 | 22   | GPIOD IRQn | 0x0000 0058 |

|       |    |                         |             |

|-------|----|-------------------------|-------------|

| IRQ7  | 23 | GPIOE_IRQHandler        | 0x0000 005C |

| IRQ8  | 24 | WKPND_IRQHandler        | 0x0000 0060 |

| IRQ9  | 25 | TIM0_IRQHandler         | 0x0000 0064 |

| IRQ10 | 26 | TIM1_IRQHandler         | 0x0000 0068 |

| IRQ11 | 27 | TIM2_IRQHandler         | 0x0000 006C |

| IRQ12 | 28 | TIM3_IRQHandler         | 0x0000 0070 |

| IRQ13 | 29 | TIM4_IRQHandler         | 0x0000 0074 |

| IRQ14 | 30 | TIM5_IRQHandler         | 0x0000 0078 |

| IRQ15 | 31 | -                       | 0x0000 007C |

| IRQ16 | 32 | -                       | 0x0000 0080 |

| IRQ17 | 33 | ADKEY_IRQHandler        | 0x0000 0084 |

| IRQ18 | 34 | POWER_UPDATE_IRQHandler | 0x0000 0088 |

| IRQ19 | 35 | CRC_DMA_IRQHandler      | 0x0000 008C |

| IRQ20 | 36 | WDT_IRQHandler          | 0x0000 0090 |

| IRQ21 | 37 | RTCC_IRQHandler         | 0x0000 0094 |

| IRQ22 | 38 | LCD_FRAME_IRQHandler    | 0x0000 0098 |

| IRQ23 | 39 | COMP_IRQHandler         | 0x0000 009C |

| IRQ24 | 40 | -                       | 0x0000 00A0 |

| IRQ25 | 41 | -                       | 0x0000 00A4 |

| IRQ26 | 42 | -                       | 0x0000 00A8 |

| IRQ27 | 43 | -                       | 0x0000 00AC |

| IRQ28 | 44 | -                       | 0x0000 00B0 |

| IRQ29 | 45 | -                       | 0x0000 00B4 |

| IRQ30 | 46 | -                       | 0x0000 00B8 |

| IRQ31 | 47 | -                       | 0x0000 00BC |

## 6.4 外部中断/事件控制器(EXTI)

外部中断和事件控制器(EXTI)管理外部和内部异步事件/中断，并生成相应的事件请求到 CPU/中断控制器和到电源管理的唤醒请求。每个输入线可以独立地配置输入类型(脉冲或挂起)和对应的触发事件(上升沿或下降沿或者双边沿都触发)。每个输入线都可以独立地被屏蔽。挂起寄存器保持着状态线的中断请求。

### 6.4.1 主要特征

EXTI 控制器的主要特性如下：

- 每个中断/事件都有独立的触发和屏蔽

- 每个中断线都有专用的状态位

- 支持多达 27 个软件的中断/事件请求

- 检测脉冲宽度低于 APB0 时钟宽度的外部信号。参见用户手册中电气特性部分的相关参数。

### 6.4.2 唤醒事件管理

JS32L010 可以处理外部或内部事件来唤醒内核(WFE)。唤醒事件可以通过下述配置产生：

- 外设的控制寄存器使能一个中断，但不在 NVIC 中使能，同时在 CPU 的系统控制寄存器中使能 SEVONPEND 位。当 CPU 从 WFE 恢复后，需要清除相应外设的中断挂起位和外设 NVIC 中断通道挂起位(在 NVIC 中断清除挂起寄存器中)。

- 配置一个外部或内部 EXTI 线为事件模式，当 CPU 从 WFE 恢复后，因为对应事件线的挂起位没有被置位，不必清除相应外设的中断挂起位或 NVIC 中断通道挂起位。

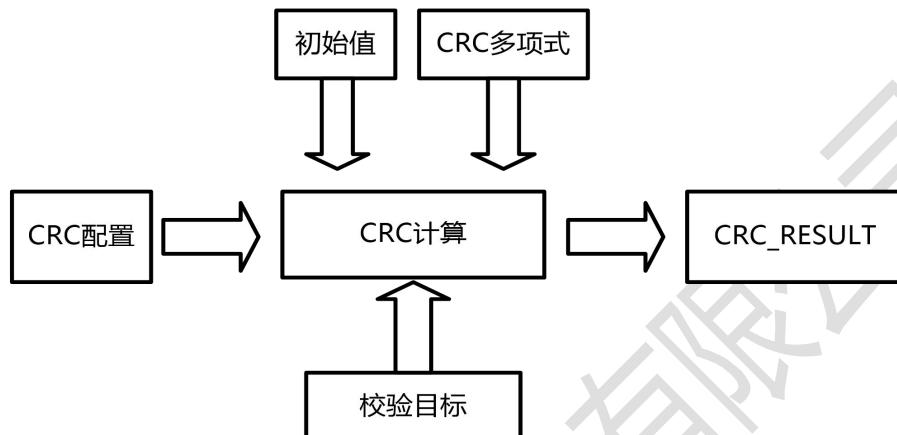

## 7 循环冗余校验计算单元 (CRC)

### 7.1 简介

循环冗余校验(CRC)计算单元是根据自定义的生成多项式得到任意一个 32 位全字的 CRC 计算结果。在其他的应用中，CRC 技术主要应用于核实数据传输或者数据存储的正确性和完整性。CRC 计算单元可以在程序运行时计算出软件的标识，之后与在连接时生成的参考标识比较，然后存放在指定的存储器空间。

### 7.2 模块框图

图 7-1 CRC 框图

### 7.3 主要特性

- 支持 5/7/8/16/32 位等不同长度的多项式

- 支持自定义的多项式

- 默认是 32 位多项式:

- $x^{32} + x^{26} + x^{23} + x^{22} + x^{16} + x^{12} + x^{11} + x^{10} + x^8 + x^7 + x^5 + x^4 + x^2 + x + 1$

- 一个 32 位初始值配置寄存器用于输入，一个 32 位结果寄存器用于输出结果

### 7.4 寄存器定义

#### 7.4.1 控制配置寄存器 (CRC\_CFG)

Address offset: 0x00

| Width | Name         | Reset | Property | Description                       |

|-------|--------------|-------|----------|-----------------------------------|

| 31:14 | Reserved     | -     | -        | -                                 |

| 13:8  | POLY_WIDTH   | 6'h20 | RW       | 支持 5/7/8/16/32 等不同长度的多项式          |

| 7:2   | Reserved     | -     | -        | -                                 |

| 1     | BIT_ORDER_EN | 1'b0  | RW       | 输入数据的顺序<br>0: 表示低位在右<br>1: 表示低位在左 |

| 0     | INT_EN       | 1'b0  | RW       | CRC 中断<br>0: 不使能<br>1: 使能         |

#### 7.4.2 初始值配置寄存器(CRC\_INIT)

Address offset: 0x04

| Width | Name       | Reset            | Property | Description |

|-------|------------|------------------|----------|-------------|

| 31:0  | INIT_VALUE | 32'hFFFFF<br>FFF | RW       | CRC 初始值     |

#### 7.4.3 取反寄存器(CRC\_INV)

Address offset: 0x08

| Width | Name      | Reset            | Property | Description |

|-------|-----------|------------------|----------|-------------|

| 31:0  | INV_VALUE | 32'hFFFFF<br>FFF | RW       | CRC 输出结果取反  |

#### 7.4.4 多项式配置寄存器(CRC\_POLY)

Address offset: 0x0C

| Width | Name       | Reset            | Property | Description          |

|-------|------------|------------------|----------|----------------------|

| 31:0  | POLY_VALUE | 32'hEDB8<br>8320 | RW       | CRC 多项式, 默认为 32 位多项式 |

#### 7.4.5 触发寄存器(CRC\_KST)

Address offset: 0x10

| Width | Name        | Reset | Property | Description |

|-------|-------------|-------|----------|-------------|

| 31:1  | Reserved    | -     | -        | -           |

| 0     | PENDING_CLR | 1'b0  | WO       | 清除 CRC 状态位  |

#### 7.4.6 状态寄存器(CRC\_STA)

Address offset: 0x14

| Width | Name     | Reset | Property | Description |

|-------|----------|-------|----------|-------------|

| 31:1  | Reserved | -     | -        | -           |

| 0     | PENDING  | 1'b0  | RO       | CRC 状态位     |

#### 7.4.7 地址寄存器(CRC\_ADDR)

Address offset: 0x1C

| Width | Name           | Reset | Property | Description                                                     |

|-------|----------------|-------|----------|-----------------------------------------------------------------|

| 31:0  | DMA_ADDR_START | 32'h0 | RO       | CRC DMA 开始的物理地址(WORD 对齐)<br>注意: 物理地址, 比如地址为 0x0 重定向 0x2000 0000 |

#### 7.4.8 长度寄存器(CRC\_LEN)

Address offset: 0x20

| Width | Name    | Reset | Property | Description |

|-------|---------|-------|----------|-------------|

| 31:0  | DMA_LEN | 32'h0 | RW       | CRC DMA 长度  |

#### 7.4.9 结果寄存器(CRC\_OUT)

Address offset: 0x24

| Width | Name    | Reset | Property | Description |

|-------|---------|-------|----------|-------------|

| 31:0  | CRC_OUT | 32'h0 | RO       | CRC 输出结果    |

### 7.5 操作流程

- 配置 CRC 初始值(CRC\_INIT)和取反(CRC\_INV)。

- 配置 CRC 多项式(CRC\_POLY), CRC 多项式的位宽(POLY\_WIDTH), 输入数据的顺序(BIT\_ORDER\_EN)。

- 配置 DMA 的开始地址(物理地址), 最后配置 DMA 的长度, 一旦长度不为 0, 即开始执行 CRC 校验。

- 等待 CRC 的 Pending(CRC\_STA), 清除 Pending(CRC\_KST), 最后得到 CRC 的结果(CRC\_OUT)。

珠海巨晟科技股份有限公司

## 8 电源管理 (POWER MANAGEMENT)

### 8.1 电源

芯片的工作电压为 1.8-3.6V。本芯片采用 Cap-Less 设计，无需在内置 LDO 输出上外挂电容。内置 LDO 具有 2 挡位下拉电流使能 PMUCON0[18:17]，同时也有过流保护功能寄存器 PMUCON0[16]，内部逻辑系统电流超过 250mA 属于异常判断。

#### 8.1.1 电压调节器

复位后调节器总是使能的。在需要低功耗的场合，可以使能低功耗工作模式。

### 8.2 电源管理器

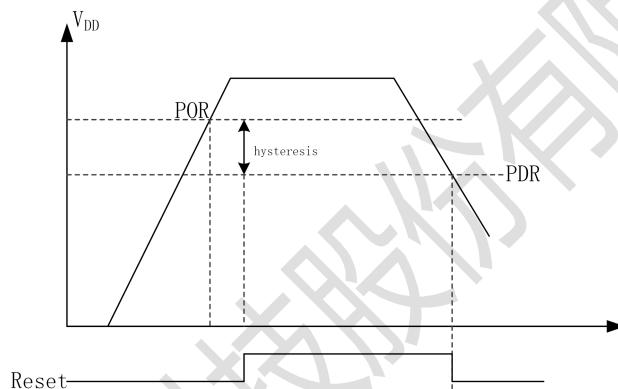

#### 8.2.1 上电复位(POR) 和掉电复位(PDR)

JS32L010 内部有一个完整的上电复位(POR)和掉电复位(PDR) 电路，当供电电压达到 1.8V 时系统即能正常工作。当 VDD 低于指定的限位电压 VPOR/VPDR 时，系统保持为复位状态，无需外部复位电路。

图 8-1 上下电复位波形图

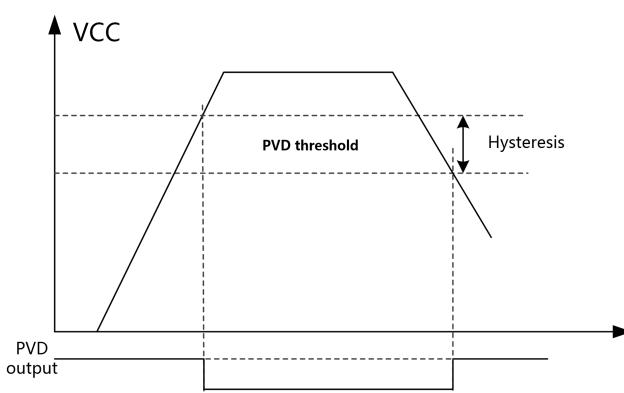

#### 8.2.2 可编程电压监测器(PVD)

JS32L010 内部集成两个电压检测器，一个检测外部供电 VCC，一个检测内部 LDO 输出 VDD，LDO 采用 Cap-Less 结构，封装上 VDD 不可见。两种检测电压均阈值可选。当系统监测到 VCC 或 VDD 电压低于配置电压值时，可以选择触发系统复位或通过使能 PVD 中断进入中断子函数。这一特性可用于执行紧急关闭任务。检测信号可以选择经过毛刺滤波电路或直接检测，由 LVDCON 的 LVD\_VCC\_BPS\_EN 和 LVDCON 的 LVD\_VDD\_BPS\_EN 来控制。

图 8-2 掉电检测波形图

## 8.3 电源控制寄存器

### 8.3.1 寄存器: LVDCON

Address: 0x4000A100

| Width | Name                 | Reset   | Property | Description                                                                 |

|-------|----------------------|---------|----------|-----------------------------------------------------------------------------|

| 31    | LVD_VDD_PENDING      | 1'b0    | RW       | VDD 电压低于设定阈值触发 PENDING, 写 0 清除                                              |

| 30    | LVD_VCC_PENDING      | 1'b0    | RW       | VCC 电压低于设定阈值触发 PENDING, 写 0 清除                                              |

| 29    | LVD_OCP_PENDING      | 1'b0    | RW       | VDD LDO 电流超出保护范围触发 PENDING, 写 0 清除                                          |

| 28:22 | LVD_VDD_DBs_LO_LIMIT | 7'h0    | RW       | 对 LVD_VDD 信号的低电平毛刺滤波宽度, 单位为系统时钟周期。                                          |

| 21:15 | LVD_VDD_DBs_HI_LIMIT | 7'h0    | RW       | 对 LVD_VDD 信号的高电平毛刺滤波宽度, 单位为系统时钟周期                                           |

| 14    | LVD_VCC_SYNC_DIS     | 1'b0    | RW       | 检测到 VCC 低电压信号触发 GPIO 复位是否需要同步<br>0: 需要同步<br>1: 不同步                          |

| 13    | LVD_VDD_BPS_EN       | 1'b0    | RW       | 屏蔽对 VDD 电压状态信号的 DEBOUNCE 滤波处理<br>0: 不使能<br>1: 使能                            |

| 12    | LVD_VCC_BPS_EN       | 1'b0    | RW       | 屏蔽对 VCC 电压状态信号的 DEBOUNCE 滤波处理<br>0: 不使能<br>1: 使能                            |

| 11    | LVD_OE               | 1'b1    | RW       | 使能阈值判断触发条件后中断, 以及复位功能<br>0: 不使能<br>1: 使能                                    |

| 10    | LVD_VDD_RST_EN       | 1'b1    | RW       | VDD 阈值判断触发后复位系统使能<br>0: 中断, 不复位<br>1: 复位, 不中断                               |

| 9     | LVD_VCC_RST_EN       | 1'b1    | RW       | VCC 阈值判断触发后复位系统使能<br>0: 中断, 不复位<br>1: 复位, 不中断                               |

| 8     | LVD_OCP_INT_EN       | 1'b0    | RW       | 过流保护信号产生中断使能<br>0: 不使能<br>1: 使能                                             |

| 7     | LVD_OCP_BPS_EN       | 1'b0    | RW       | 屏蔽对过流保护信号的消抖处理<br>0: 不使能<br>1: 使能                                           |

| 6:3   | H_LVD_S              | 4'b0100 | RW       | VCC LVD 设置(单位 V):<br>b0000: 1.5<br>b0001: 1.55<br>b0010: 1.6<br>b0011: 1.65 |

|   |          |      |    |                                                                                                                                                                       |

|---|----------|------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |          |      |    | b0100: 1.7<br>b0101: 1.75<br>b0110: 1.8<br>b0111: 1.9<br>b1000: 2.0<br>b1001: 2.1<br>b1010: 2.2<br>b1011: 2.3<br>b1100: 2.4<br>b1101: 2.5<br>b1110: 2.6<br>b1111: 2.7 |

| 2 | L_LVD_S  | 1'b0 | RW | VDD LVD 检测设置(单位 V)<br>0: 1.25<br>1: 1.35                                                                                                                              |

| 1 | L_LVD_EN | 1'b1 | RW | VDD LVD 使能<br>0: 不使能<br>1: 使能                                                                                                                                         |

| 0 | HLVD_EN  | 1'b1 | RW | VCC LVD 使能<br>0: 不使能<br>1: 使能                                                                                                                                         |

### 8.3.2 寄存器 LVDCON1

Address: 0x4000A104

| Width | Name                | Reset | Property | Description                        |

|-------|---------------------|-------|----------|------------------------------------|

| 31    | Reserved            | -     | -        | -                                  |

| 30:24 | OCP_DBs_LO_LIMIT    | 7'h0  | RW       | 对过流保护信号的低电平毛刺滤波宽度, 单位为系统时钟周期。      |

| 23    | Reserved            | -     | -        | -                                  |

| 22:16 | OCP_DBs_HI_LIMIT    | 7'h0  | RW       | 对过流保护信号的高电平毛刺滤波宽度, 单位为系统时钟周期。      |

| 15    | Reserved            | -     | -        | -                                  |

| 14:8  | LVDVCC_DBs_LO_LIMIT | 7'h0  | RW       | 对 LVD VCC 信号的低电平毛刺滤波宽度, 单位为系统时钟周期。 |

| 7     | Reserved            | -     | -        | -                                  |

| 6:0   | LVDVCC_DBs_HI_LIMIT | 7'h0  | RW       | 对 LVD VCC 信号的高电平毛刺滤波宽度, 单位为系统时钟周期。 |

## 9 低功耗(LOW POWER)

### 9.1 低功耗模式

在系统或电源复位以后，微控制器处于正常模式运行状态，系统所用时钟为 128KHz 内部 RC 振荡器输出。当 CPU 不需继续运行时，可以利用进入多种低功耗模式来节省功耗。例如等待某个外部事件时，用户需要根据最低电源消耗、最快启动时间和可用的唤醒源等条件，选定一个最佳的低功耗模式。

三种低功耗模式：

- 待机模式(Idle Mode)

- 停止模式(Stop Mode)

- 睡眠模式(Sleep Mode)

表 9-1 低功耗模式说明

| 待机模式(Idle Mode)    | 停止模式(Stop Mode)              | 睡眠模式(Sleep Mode)                |

|--------------------|------------------------------|---------------------------------|

| -                  | 数字模块时钟停止                     | 数字模块时钟停止                        |

| -                  | 可选：片内 26M 时钟源关闭(设置 LPCON[3]) | 可选：片内 26MHz 时钟源关闭(设置 LPCON[3])  |

| -                  | 可选：SRAM 关闭(设置 LPCON[2])      | 可选：SRAM 关闭(设置 LPCON[2])         |

| -                  | -                            | 可选：片内 128KHz 时钟源关闭(设置 LPCON[4]) |

| -                  | -                            | 可选：PMU 进入低功耗模式(设置 LPCON[7])     |

| -                  | FLASH 进入普通睡眠模式               | FLASH 进入深度睡眠模式(功耗更低)            |

| -                  | -                            | 可选：唤醒后复位(设置 SYSCON0[30])        |

| CPU 停止             | CPU 停止                       | CPU 停止                          |

| _ASM("WFI")指令进入该模式 | 配置 LPCON[1]进入该模式             | 配置 LPCON[0]进入该模式                |

注：可以通过关闭未使用的外设、时钟源使功耗降到最低。

此外，在运行模式下，可以通过以下方式中的一种降低功耗：

- 降低系统时钟

- 关闭 APB 和 AHB 总线上未被使用的外设时钟。

- 合理配置 APB 与 AHB 的频率关系

### 9.2 进入低功耗

进入低功耗模式(Sleep)步骤：

- 关闭相应的模拟模块，以及 PMU 的部分功能(PMU\_BGBUF, PMU\_TSEN 等)。

- 切换系统时钟到 128KHz (依靠端口唤醒) 或者 32KHz (只依靠其它源唤醒)，并且关闭其它时钟源。

- 配置 PMU 全面进入低功耗。

- 关闭 LCD(若有 LCD)模拟模块的一些非必要功能 (VFBDET\_EN,VTEST\_EN,VDET\_EN，这些功能默认是关闭的)。

- 无用的 IO 都设成模拟模式。

- 进入 Sleep 前的数字准备 (配置唤醒源，使能 WKUP\_EN，初始化 WKPND\_IRQn，关闭看门狗，使能进入 Sleep 时自动关闭 128KHz 内部 RC 振荡器的选项，使能 SLEEP\_GOON\_EN 唤醒时不复位)。

- 配置 LP\_CON0[0]进入 Sleep。

### 9.3 低功耗唤醒

支持多种唤醒方式：

- 端口唤醒

总共有 12 组信号源 (由 WKUP\_CON[11:0]控制使能)，每组信号源是 3~6 个 IO 的或逻辑。

这些唤醒源唤醒之后是会产生中断并且有对应的中断状态位，中断是不可屏蔽的（即有中断状态就一定有中断）。另外，由 SLEEP\_GOON\_EN (SYS\_CON0[30]) 决定用端口唤醒时是产生系统复位还是继续运行。

- 其它源唤醒

支持看门狗唤醒、比较器唤醒，RTC 唤醒、串口升级中断唤醒，LVD 唤醒，电量检测唤醒、多机通信串口唤醒。

其中串口多机通讯唤醒、比较器唤醒、电量检测唤醒与端口唤醒组 10 复用 (WKUP\_CON[10] 使能)。LVD 唤醒、RTC 唤醒与端口唤醒组 11 复用 (WKUP\_CON[11] 使能)。

珠海巨晟科技股份有限公司

## 10 复位和时钟控制 (RESET/CLOCK)

### 10.1 引脚复位(MCLR)功能

默认状态下 JS32L010 支持 MCLR 复位功能，PE2 为 MCLR 引脚，该引脚默认使能内部上拉功能，在 PE2 输入一个持续 1.7ms 以上的低电平导致系统复位，如同重新上电复位一样。用户可以通过修改 FLASH 中用户自定义位来关闭 MCLR 功能，关闭后 PE2 会变成 GPIO。详细情况请参考闪存存储器中关于用户自定义区域的描述。

### 10.2 复位

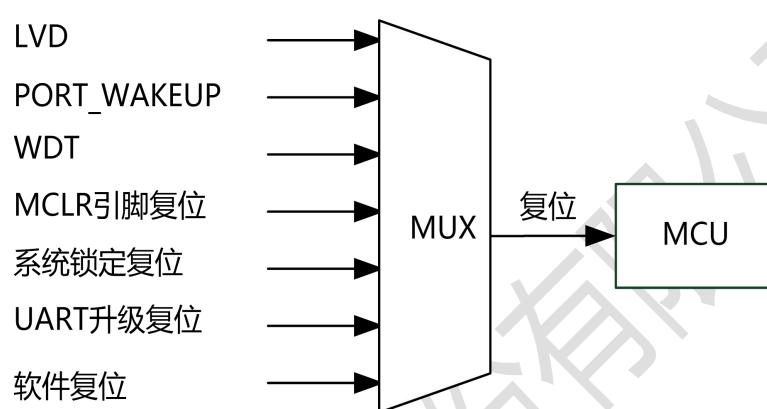

JS32L010 支持系统复位、电源复位和主复位。

图 10-1 复位源框图

#### 10.2.1 系统复位

系统复位将复位除某些复位状态寄存器和特殊功能寄存器之外的所有寄存器。

当以下事件中的一件发生时，产生一个系统复位：

- SLEEP 模式下外部 IO 口唤醒

- WDT 计数溢出复位

- UART 单线升级程序复位

- 系统锁定复位

#### 10.2.2 主复位

主复位能将部分系统复位无法复位的寄存器复位。

以下事件可以触发一个主复位：

- 软件复位

- PVD 检测到电压低事件，且控制器处于复位功能模式

- 当芯片支持 MCLR(引脚)复位时，MCLR 指在某个特定 IO 引脚上输入一个持续 1.7ms 以上的低电平导致系统复位

#### 10.2.3 电源复位

上电/掉电复位(POR/PDR 复位)都属于电源复位。电源复位将复位所有的逻辑和模拟模块。复位入口矢量被固定在地址 0x0000 0004。

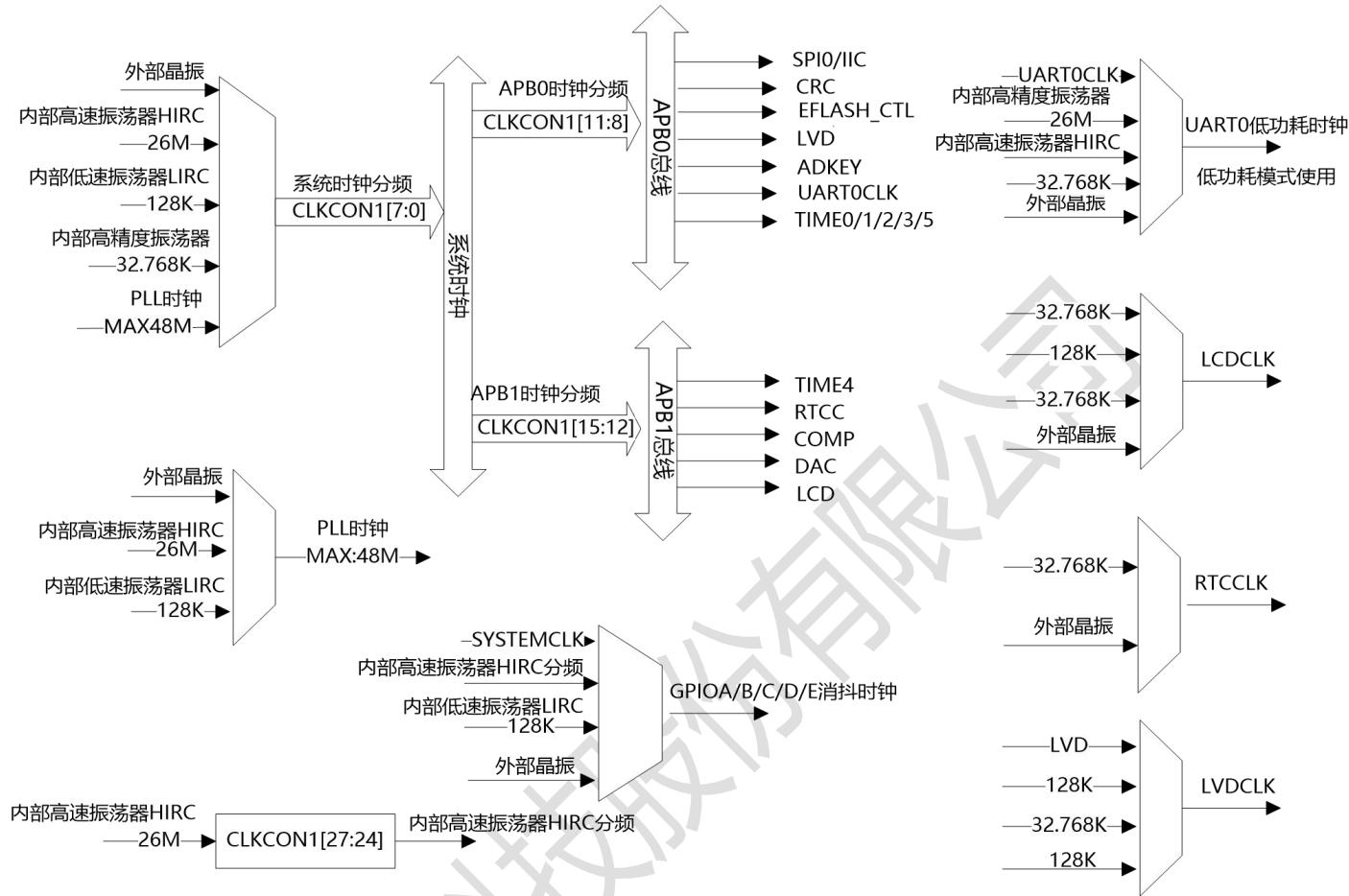

## 10.3 时钟

### 10.3.1 模块框图

图 10-2 时钟模块

### 10.3.2 XOSC 时钟

外部时钟信号(32.768KHz)由以下两种时钟源产生：

- 外部晶体/陶瓷谐振器

- 用户外部时钟

### 10.3.3 HIRC 时钟

HIRC 时钟信号由内部 26MHz 的振荡器产生，可直接作为系统时钟或作为 PLL 输入。 HIRC 振荡器能够在不需要任何外部器件的条件下提供系统时钟。 HIRC 的启动时间比 XOSC 晶体振荡器短，需要频率校准，校准值写在 FLASH 系统存储区域。在程序使用这个时钟前，可以读取并配置出高精度的 HIRC 时钟。经过出厂效验后，正常温度范围内 HIRC 精度为 26MHz( $\pm 1.5\%$ )，具体请参考电气特性参数。

系统内置时钟安全系统，如果 XOSC 晶体振荡器失效，切换到高精度 32KHz。

### 10.3.4 PLL 时钟

内部 PLL 可以选择内部高精度 32KHz RC 振荡器、内部 26MHz、外部 32KHz 晶振作为参考时钟，支持小数分频。进一步信息请参考第二十章。

### 10.3.5 LIRC 时钟

LIRC 振荡器担当一个低功耗时钟源的角色，它作为系统启动时钟为其他单元提供时钟。 LIRC 时钟频率大约 128KHz。

### 10.3.6 内部高精度 32K

高精度 32KHz 振荡器担当一个高精度时钟源的角色, 它主要为 RTC,LCD 提供时钟。大约 32.768KHz, 具体精度参考电气参数。

### 10.3.7 系统时钟 (SYSCLK)

五种不同的时钟源可被用来驱动系统时钟(SYSCLK):

- 内部低速 128KHz LIRC

- 内部高速 26MHz( $\pm 1.5\%$ ) 高速振荡器

- 内部高精度 32.768KHz( $\pm 1.5\%$ ) 低功耗低速振荡器

- 片内高速 PLL 时钟

- 支持外部 32.768KHz 晶体振荡器(内置电容)

### 10.3.8 毛刺滤波时钟源选择

三种不同的时钟源可被用来驱动 GPIO 的毛刺滤波时钟:

- 内部高速 26MHz HIRC 的分频时钟

- 系统时钟

- 内部低速 128KHz LIRC

当不被使用时, 任一个时钟源都可被独立地启动或关闭, 由此优化系统功耗。

### 10.3.9 时钟安全系统(CSS)

时钟安全系统可以通过软件被激活。在使用这个功能时, 请确保 XOSC 已经被成功使能。如果 XOSC 时钟发生故障, 产生时钟安全中断 CSSI, 允许软件完成营救操作。此 CSSI 中断连接到 CPU 的 NMI 中断。

注: 一旦 CSS 被激活, 并且 XOSC 时钟出现故障, CSS 中断就产生, 并且 NMI 也自动产生。NMI 将被不断执行, 直到 CSS 中断挂起位被清除。因此, 在 NMI 的处理程序中必须通过设置时钟中断寄存器, (HOSC\_MNT) 里的 HOSC\_LOSS\_PENDING 位写 1 来清除 CSS 中断。通过寄存器使能, 时钟故障将导致内部 XOSC 时钟自动切换到内部高精度 32KHz。

## 11 通用输入输出 (GPIO)

### 11.1 简介

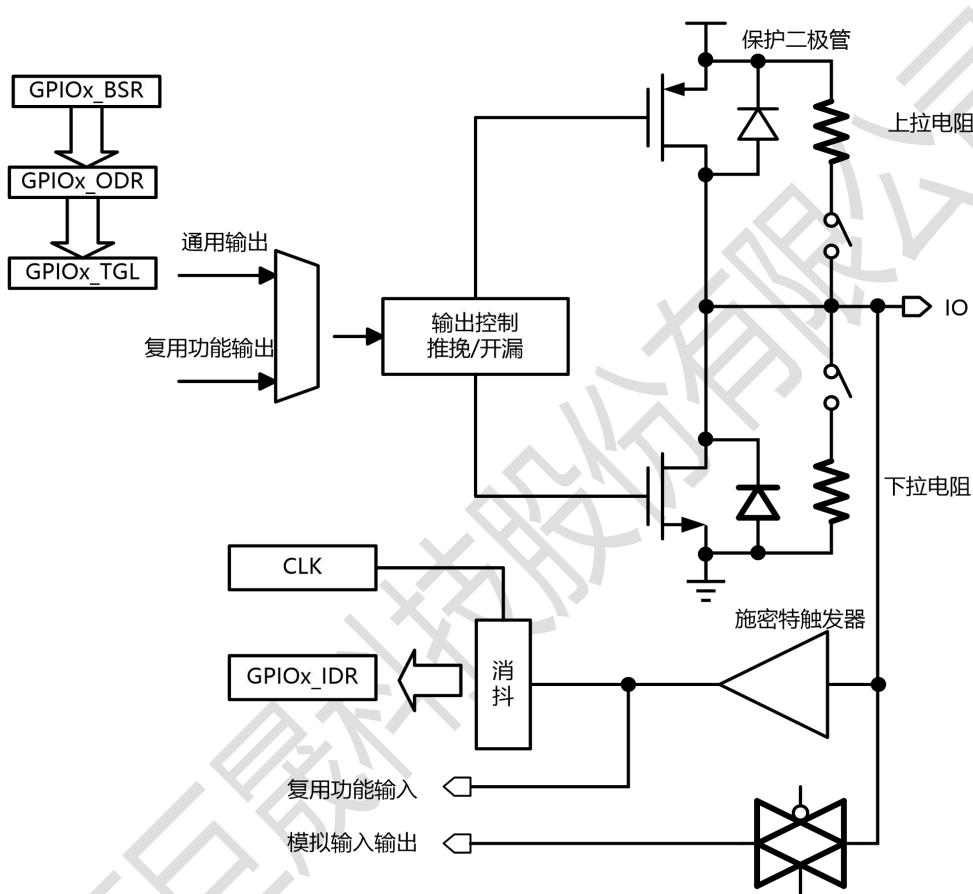

每组 GPIO 端口有四个 32 位配置寄存器(GPIOx\_MODER, GPIOx\_OTYPER, GPIOx\_OSPEEDR and GPIOx\_PUPDR), 两个 32 位数据寄存器(GPIOx\_IDAT and GPIOx\_ODAT), 一个 32 位置位/复位寄存器(GPIOx\_BSR) 和一个 32 位翻转寄存器(GPIOx\_TGL)。另外, 所有 GPIO 有一个 32 位锁定寄存器(GPIOx\_LCKR) 和两个复用功能选择寄存器 (GPIOx\_AFRH and GPIOx\_AFRL)。

注: GPIOx 中的 x 表示 GPIO 组数。LQFP48 封装, x 代表 A, B, C, E。LQFP64 封装, x 代表 A, B, C, D, E。

### 11.2 模块框图

图 11-1 GPIO 模块框图

### 11.3 GPIO 主要特征

- 输出状态: 推挽或开漏+上下拉

- 输出寄存器状态值 (GPIOx\_ODAT) 或者复用功能输出

- 输入状态: 浮空、上下拉、模拟

- 输入数据到数据寄存器(GPIOx\_IDAT) 或复用功能输入

- 独立置位/复位/翻转 IO 状态 (GPIOx\_BSR、GPIOx\_TGL)

- 通过加锁配置 (GPIOx\_LCKR) 锁定 IO 状态

- 模拟功能

- 复用功能

### 11.4 GPIO 功能描述

GPIO 的每一个端口可以通过软件独立配置成下面状态:

- 输入浮空

- 输入上拉

- 输入下拉

- 模拟功能

- 开漏输出

- 推挽输出

- 复用功能

表 11-1 GPIO 端口位配置表

| MODE/模式 | OTYPE/输出类型 | OSPEED/驱动能力 | PUPD/上下拉 |   | IO configuration/端口配置 |        |

|---------|------------|-------------|----------|---|-----------------------|--------|

| 01      | 0          | SPEED[3:0]  | 0        | 0 | GP output             | PP     |

|         | 0          |             | 0        | 1 | Reserved              |        |

|         | 0          |             | 1        | 0 |                       |        |

|         | 0          |             | 1        | 1 |                       |        |

|         | 1          |             | 0        | 0 | GP output             | OD     |

|         | 1          |             | 0        | 1 | GP output             | OD+PU  |

|         | 1          |             | 1        | 0 | Reserved              |        |

|         | 1          |             | 1        | 1 |                       |        |

| 10      | 0          | SPEED[3:0]  | 0        | 0 | AF                    | PP     |

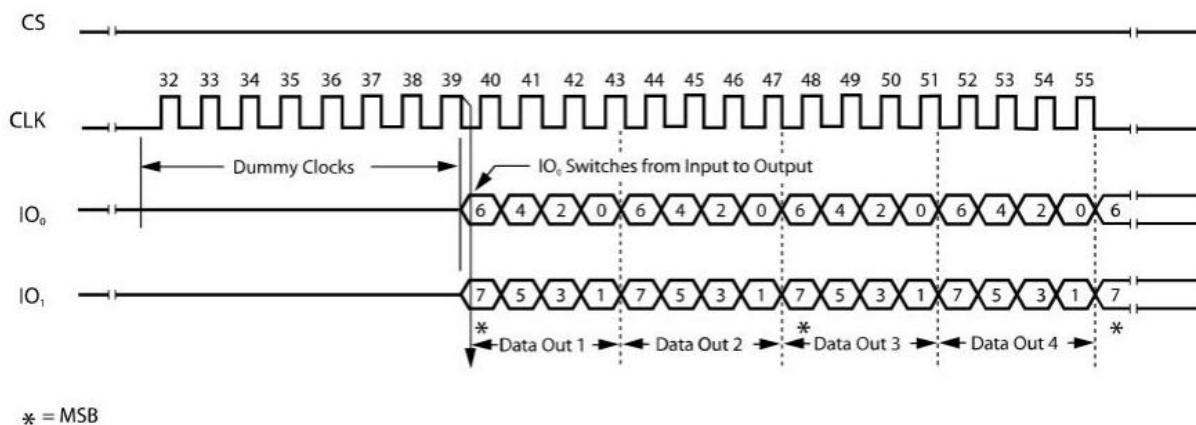

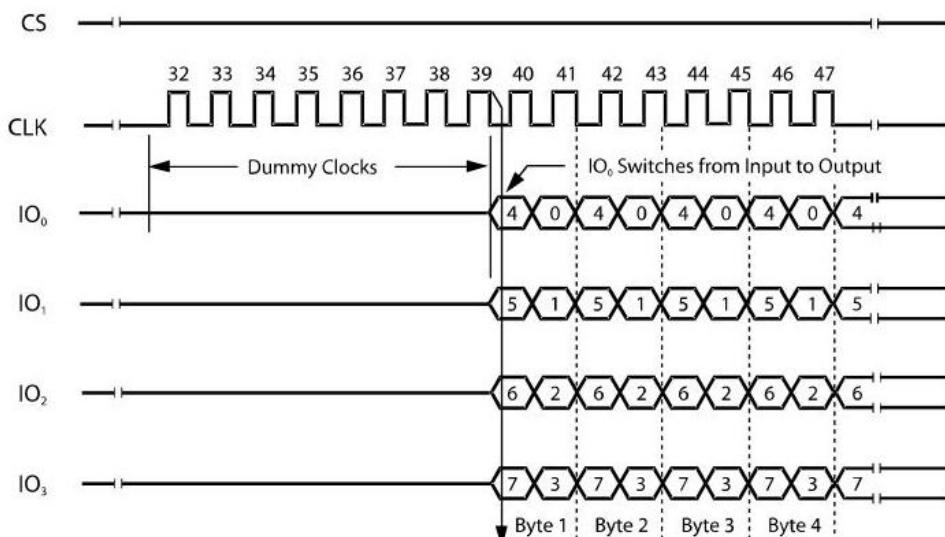

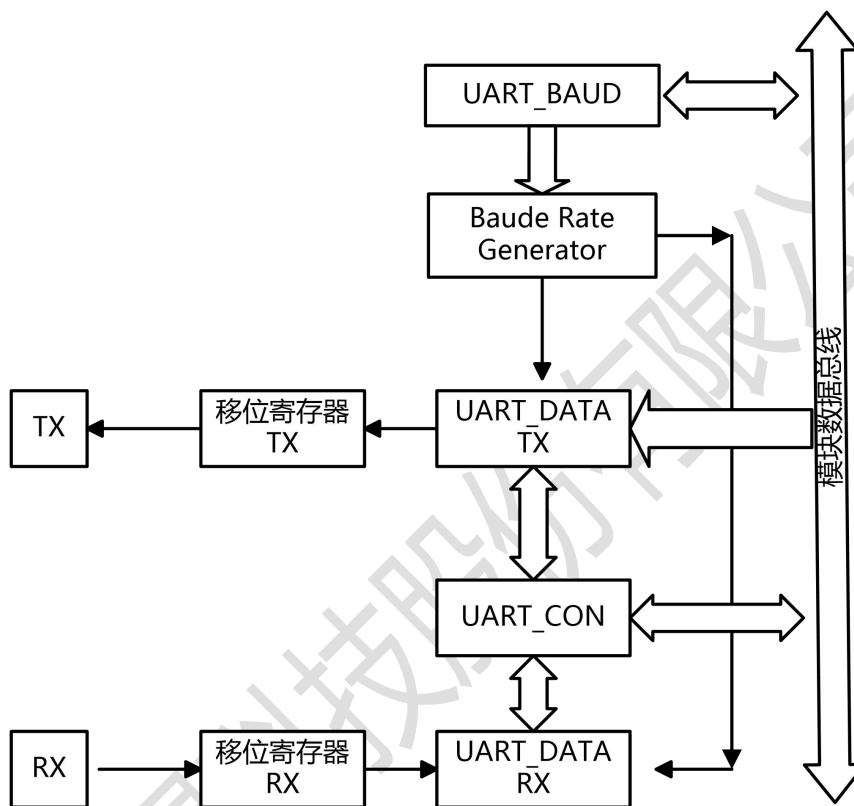

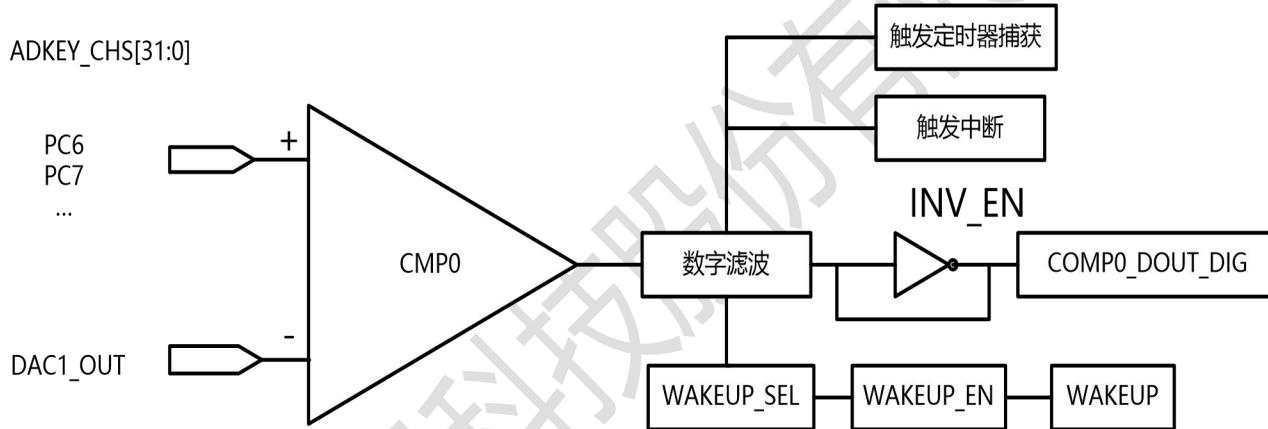

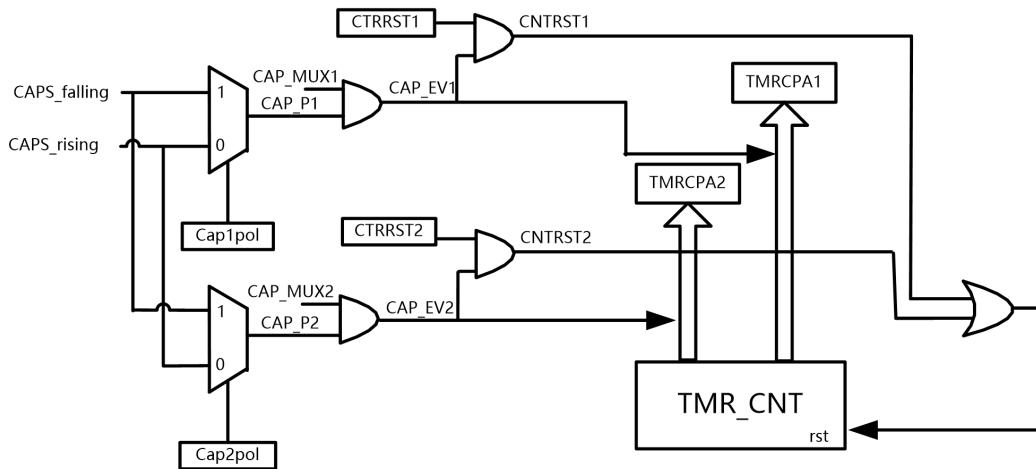

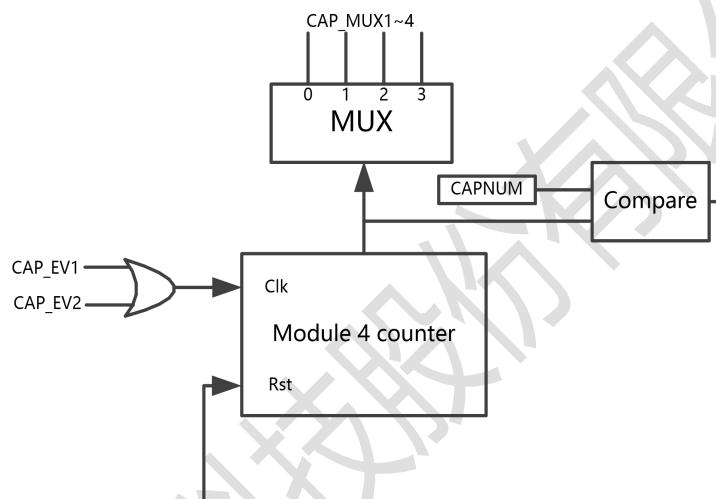

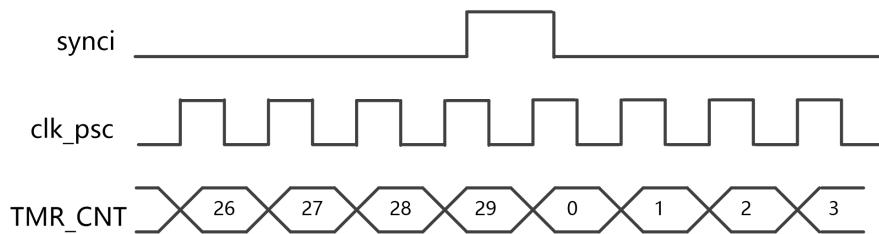

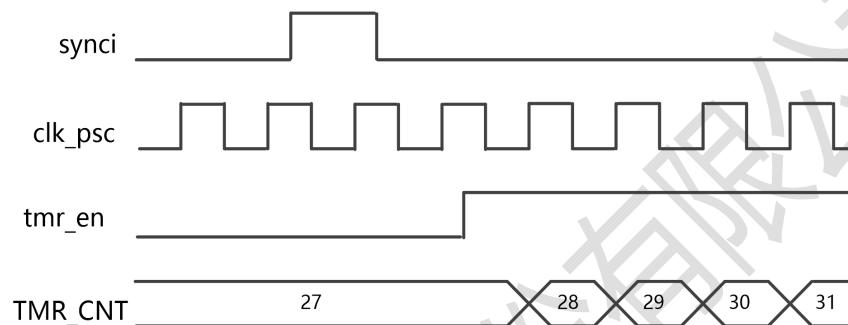

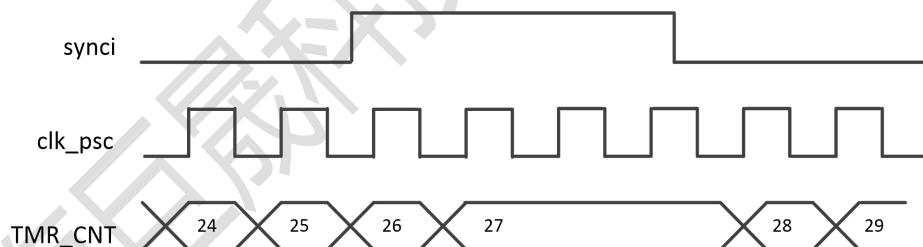

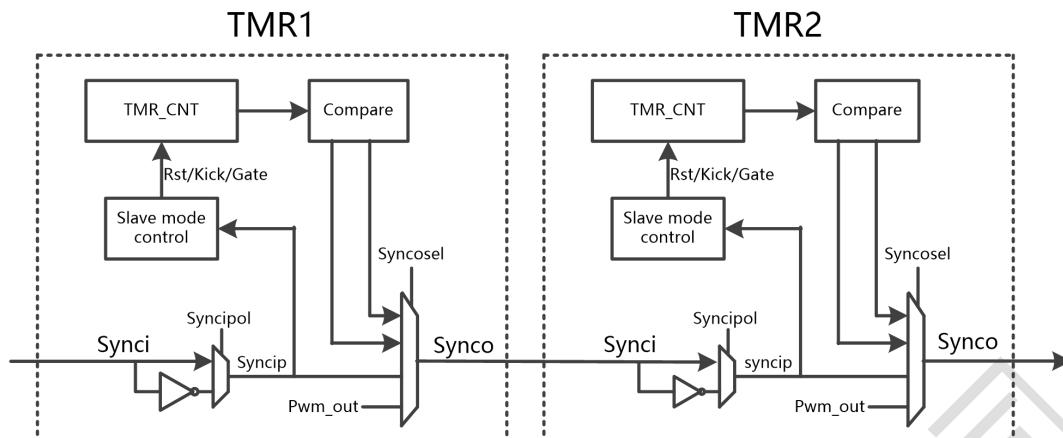

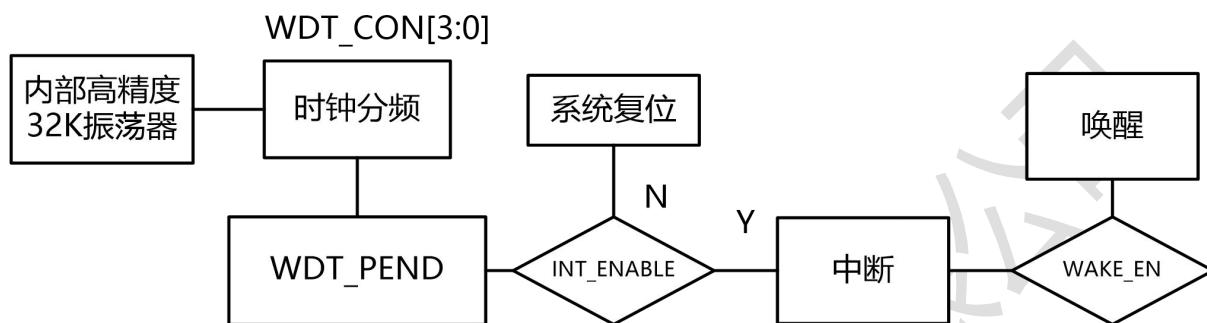

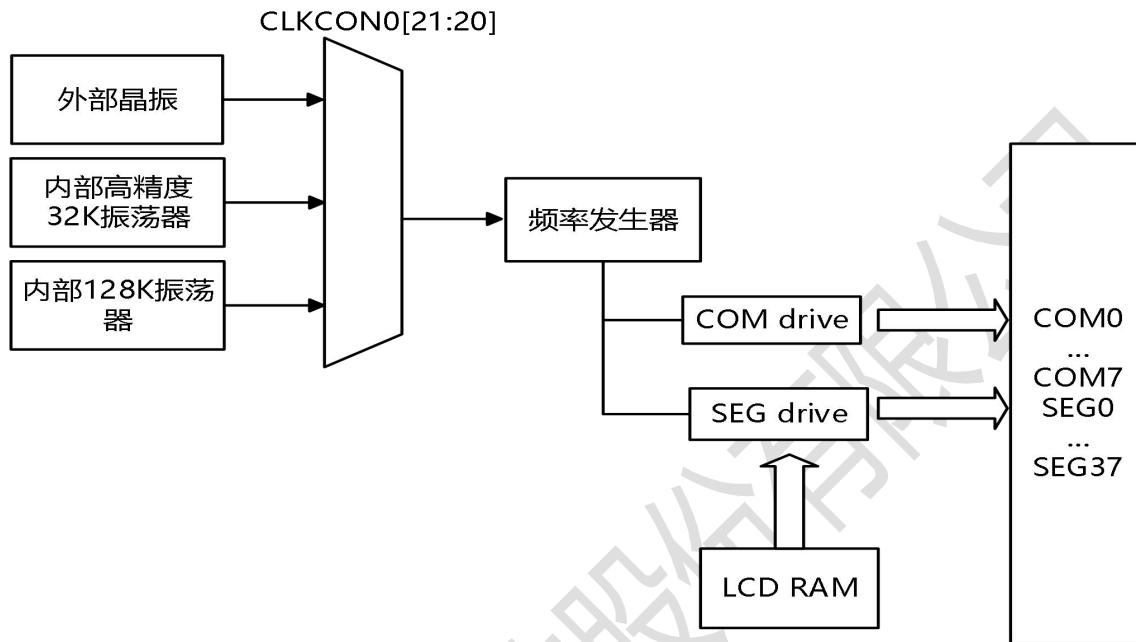

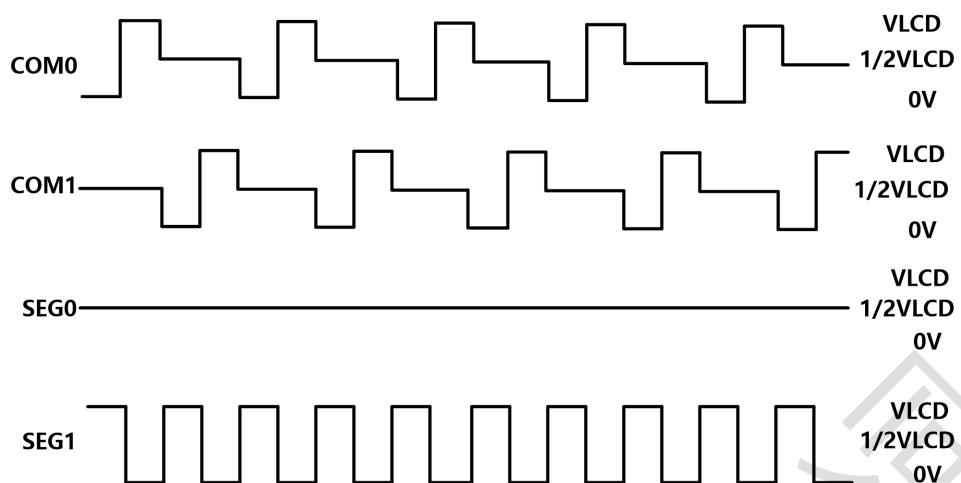

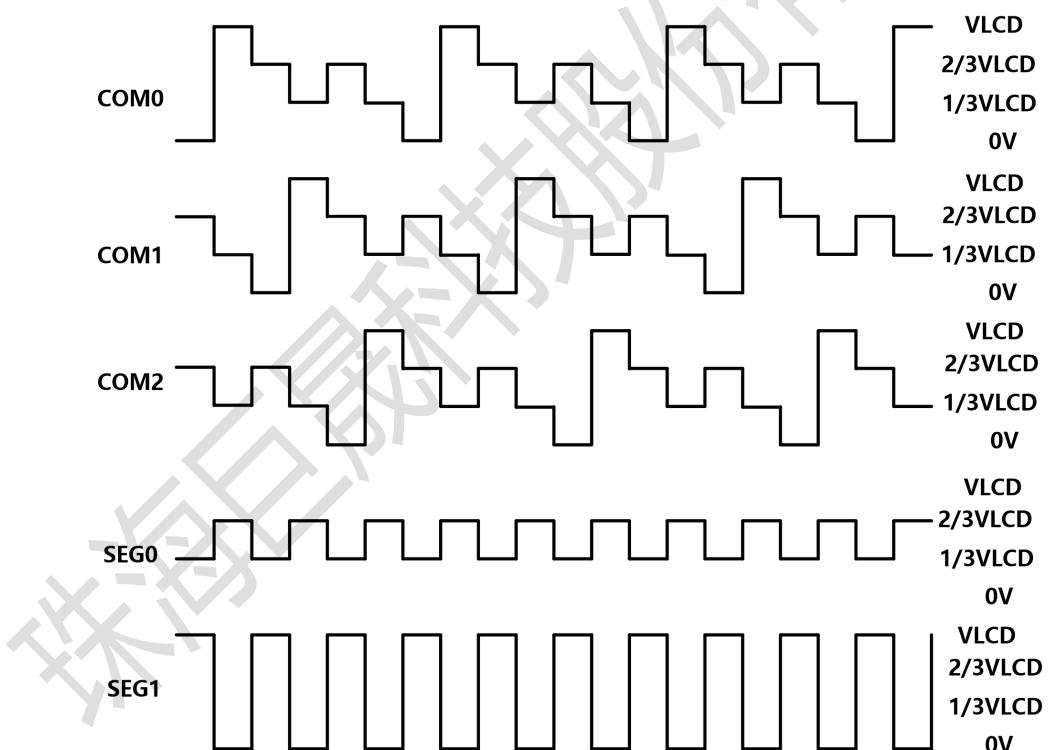

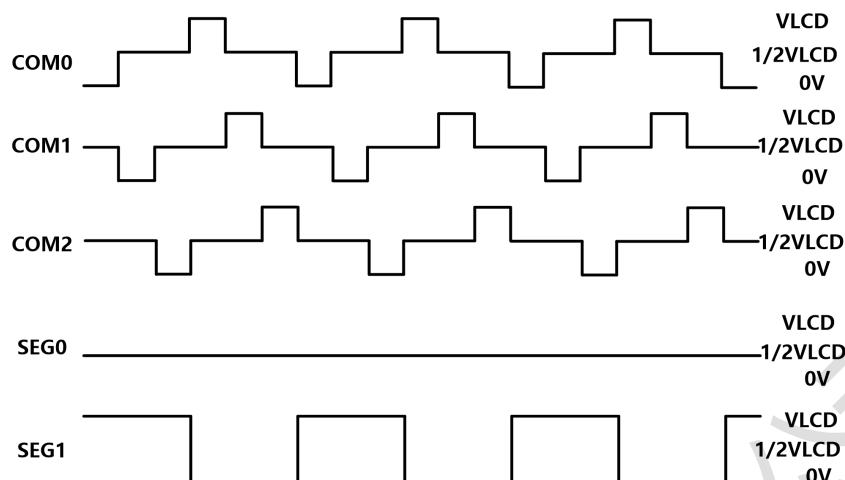

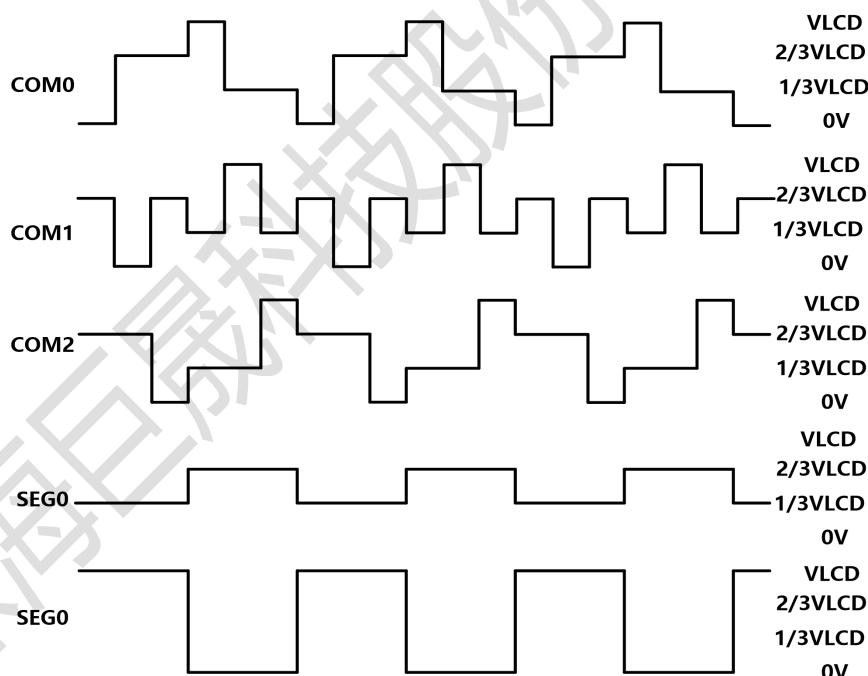

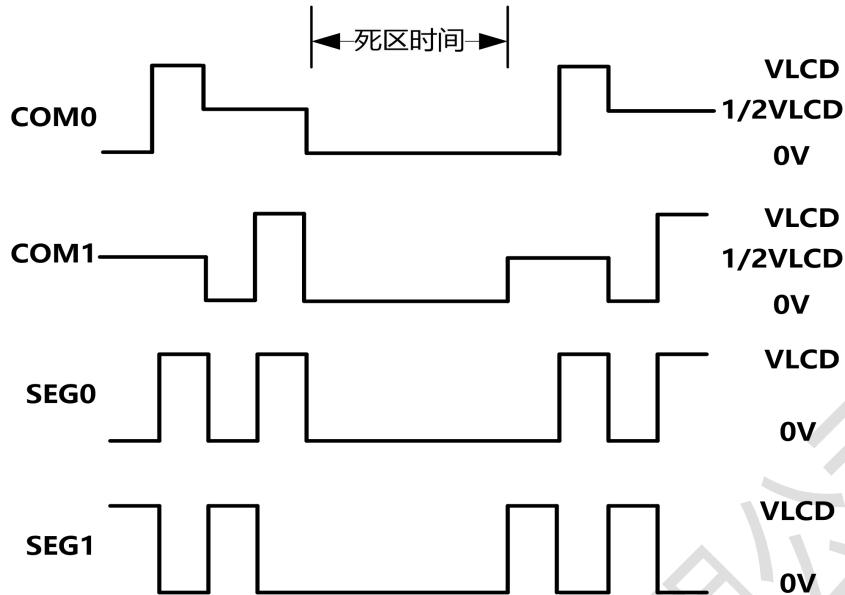

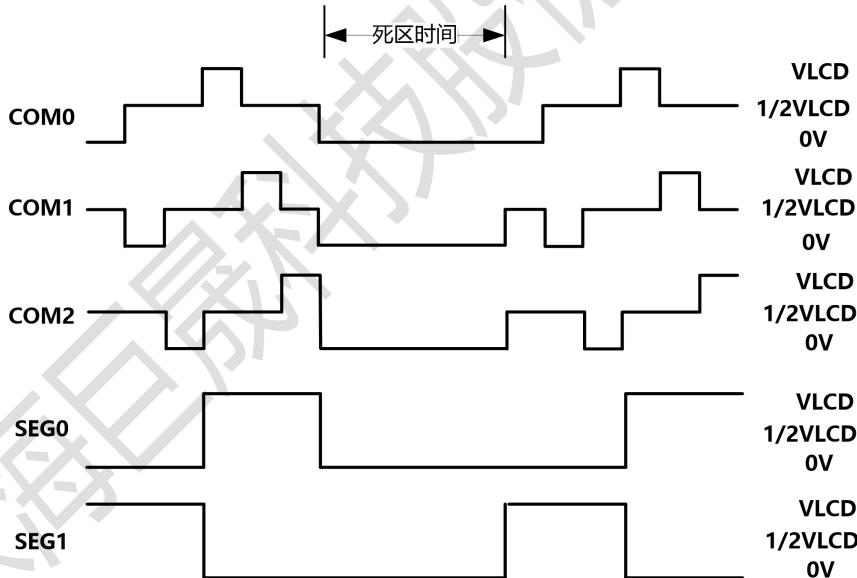

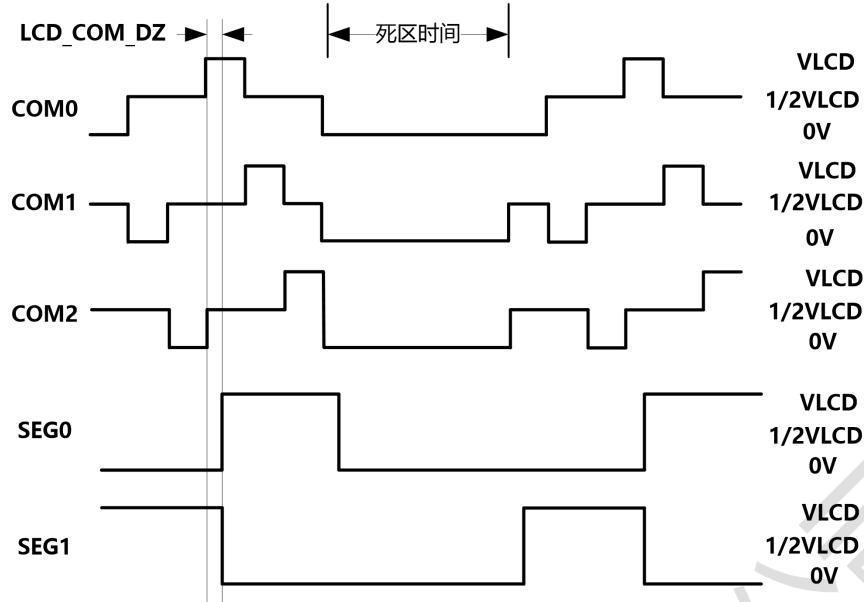

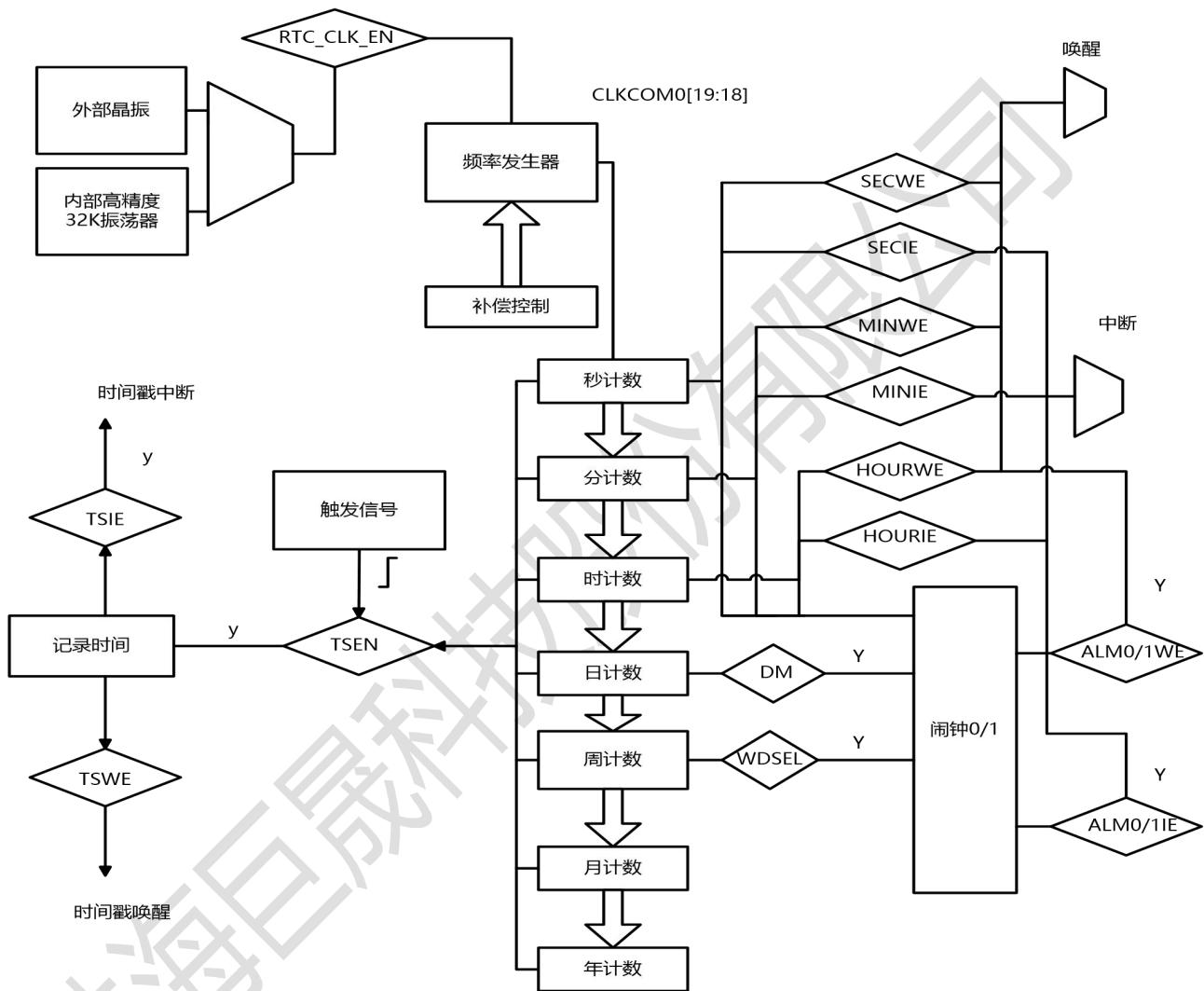

|         | 0          |             | 0        | 1 | Reserved              |        |